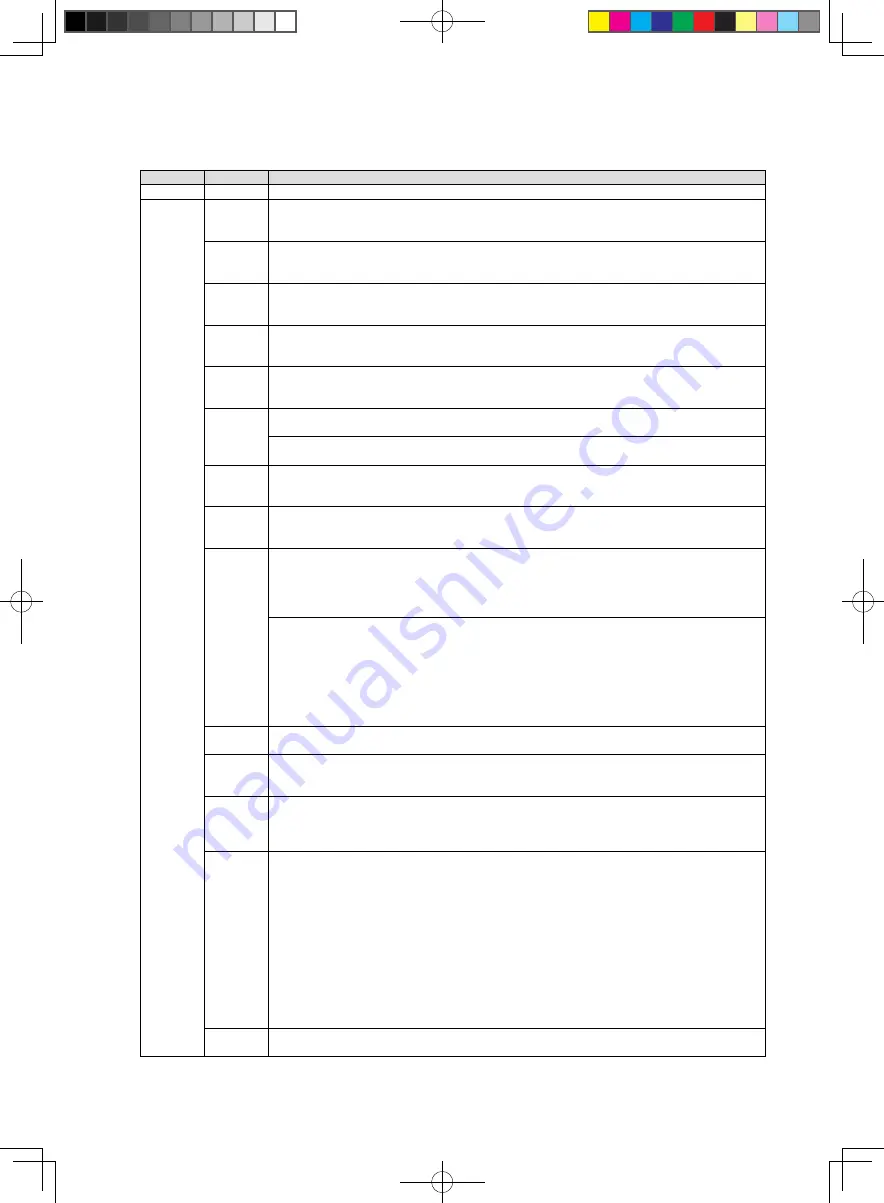

REVISION HISTORY

Revision History

Code No.

Page

Contents

411900100

All

New establishment

411900101

1-3

Features: SDRAMC

(Old) • Equipped with a two-stage

×

32-bit DQB (Data Queue Buffer).

(New) • Equipped with a four-stage

×

16-bit DQB (Data Queue Buffer).

1-5

Features: USI/USIL (SPI mode)

(Old) - Receive data mask function is available (master mode only).

(New) Deleted

1-6

Features: USB

(Old) • Scratchable variable number of bulk end points

(New) • Supports four general-purpose endpoints and endpoint 0 (control).

1-12

Pin functions: Notes on pin name

(Old) No description

(New) - Be sure to avoid assigning the same signal to more than one pin.

1-14

List of external bus pins: #CE10

(Old)

*

The #CE10 pull-up resistor enable/disable ... when the #CE10 pin is configured as an input pin.

(New)

*

The #CE10 pull-up resistor is enabled (en) ... or disabled (dis) when the BOOT pin is set to 1.

1-19

List of Other Pins: BOOT

Modified Table 1.3.2.7

USI/USIL pin configuration: USI_DO, USIL_DI, USIL_DO

Modified Tables 1.3.2.8 and 1.3.2.9

3-2

Memory map: Boot address

(Old) Note: ... Note, however, ... Connect a pull-down resistor to the #CE10 pin to set the pin level to 0.

(New) Note: ... Note, however, ... pull-up or pull-down resistor to set the #CE10 pin input level to 1 or 0.

3-3

Memory map: IVRAM

(Old) IVRAM located in Area 3 is accessed in five or six cycles, according to the ... register setting.

(New) IVRAM located in Area 3 is accessed in four or five cycles, according to the ... register setting.

4-3

Power supply: Power-on sequence

(Old) (2) t

PR

: Power-on-reset time

... See “Electrical Characteristics” for the power-on-reset time.

(New) (2) t

PR

: Power-on-reset time

... See the “#RESET Pin” section in the “Reset and NMI” chapter for the power-on-reset time.

Power supply: Power-off sequence

(Old) Power-off: ...

3. LV

DD

, PLLV

DD

(and RTCV

DD

) (May be turned off with 1 above at the same time.)

Notes: • Applying only HV

DD

makes a diode circuit on the path from HV

DD

to AV

DD

...

• Be sure to avoid applying AV

DD

... degraded due to flow-through current of the AV

DD

.

(New) Power-off: ...

3. LV

DD

, PLLV

DD

(and RTCV

DD

) (May be turned off with 2 above at the same time.)

Note: Be sure to avoid applying HV

DD

or AV

DD

... due to flow-through current of the HV

DD

or AV

DD

.

6-6

CMU: PLL setting examples

Modified Table 6.4.4.4

8-9

RTC: WAKEUP and #STBY pins

(Old) Note that leakage currents flow from the RTCV

DD

system ... the #STBY pin is set to a high level.

(New) Note that leakage current flows to the RTCV

DD

system ... the #STBY pin is set to a high level.

9-3

SRAMC: Chip enable signals

(Old) The SRAMC provides maximum 26 bits of ... access to a maximum 382M-byte address space.

(New) The SRAMC provides maximum 26 bits of ... access to a maximum 336M-byte address space.

Modified Table 9.4.1.1

9-10

SRAMC: SRAM read/write timings with external #WAIT

(Old) Note: Figures 9.6.2.1 and 9.6.2.2 assume a very low operating speed ...

• When a #CE

x

signal is used to generate a #WAIT signal, set the conditions ...

Operating clock frequency < 60 MHz:

CE

x

SETUP[1:0] = 0x1 and CE

x

WAIT[3:0] = 0x2, or ...

• When a #RD/#WRH/#WRL signal is used to generate a #WAIT signal, set the conditions ...

Operating clock frequency < 60 MHz:

CE

x

WAIT[3:0] = 0x3 ...

(New) Note: Figures 9.6.2.1 and 9.6.2.2 assume a very low operating speed ...

• When a #CE

x

signal is used to generate a #WAIT signal, set the conditions ...

CE

x

SETUP[1:0] = 0x1 and CE

x

WAIT[3:0] = 0x2, or ...

• When a #RD/#WRH/#WRL signal is used to generate a #WAIT signal, set the condition ...

CE

x

WAIT[3:0] = 0x3 ...

10-3

SDRAMC: SDRAM size selections and SDRAM address

Modified Table 10.4.2.2