117

XMEGA B [DATASHEET]

8291B–AVR–01/2013

Note:

Reserved settings will not give any timeout for the window.

Bit 1 – WEN: Window Mode Enable

This bit enables the window mode. In order to change this bit, the WCEN bit in

“WINCTRL – Window Mode Control

must be written to one at the same time. This bit is protected by the configuration change

protection mechanism. For a detailed description, refer to

“Configuration Change Protection” on page 13

Bit 0 – WCEN: Window Mode Change Enable

This bit enables the ability to change the configuration of the

“WINCTRL – Window Mode Control register” on page 116

When writing a new value to this register, this bit must be written to one at the same time for the changes to take effect.

This bit is protected by the configuration change protection mechanism, but not protected by the WDT lock fuse.

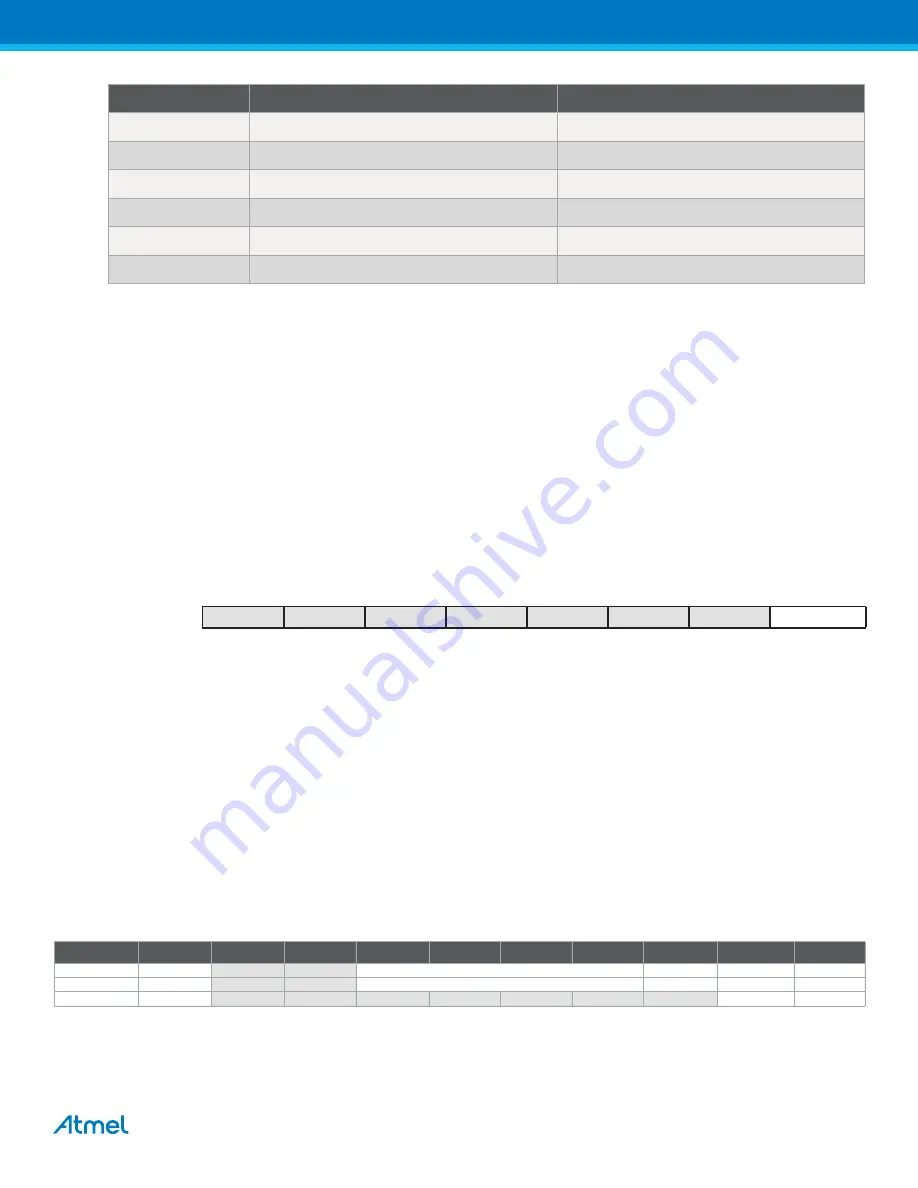

10.7.3 STATUS – Status register

Bit 7:1 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always write these bits to zero

when this register is written.

Bit 0 – SYNCBUSY: Synchronization Busy Flag

This flag is set after writing to the CTRL or WINCTRL registers and the data are being synchronized from the system

clock to the WDT clock domain. This bit is automatically cleared after the synchronization is finished. Synchronization will

take place only when the ENABLE bit for the Watchdog Timer is set.

10.8

Register Summary

1010

8KCLK

8.0s

1011

–

Reserved

1100

–

Reserved

1101

–

Reserved

1110

–

Reserved

1111

–

Reserved

WPER[3:0]

Group Configuration

Typical Closed Window Periods

Bit

7

6

5

4

3

2

1

0

–

–

–

–

–

–

–

SYNCBUSY

Read/Write R

R

R

R

R

R

R

R

Initial Value

0

0

0

0

0

0

0

0

Address

Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Page

+0x00

CTRL

–

–

PER[3:0]

ENABLE

CEN

+0x01

WINCTRL

–

–

WPER[3:0]

WEN

WCEN

+0x02

STATUS

–

–

–

–

–

–

–

SYNCBUSY

Summary of Contents for XMEGA B

Page 320: ...320 XMEGA B DATASHEET 8291B AVR 01 2013 Table 25 12 7 segments Character Table...

Page 321: ...321 XMEGA B DATASHEET 8291B AVR 01 2013 Table 25 13 14 segments Character Table...

Page 322: ...322 XMEGA B DATASHEET 8291B AVR 01 2013 Table 25 14 16 segments Character Table...

Page 412: ...412 XMEGA B DATASHEET 8291B AVR 01 2013...

Page 413: ...413 XMEGA B DATASHEET 8291B AVR 01 2013...