MC96FR116C

November, 2018 Rev.1.8

133

The Data Overrun (DOR) flag indicates data loss due to a receive buffer full condition. A DOR occurs

when the receive buffer is full, and another new data is present in the receive shift register which are

to be stored into the receive buffer. After the DOR flag is set, all the incoming data are lost. To prevent

data loss or clear this flag, read the receive buffer.

The Parity Error (PE) flag indicates that the frame in the receive buffer had a Parity Error when

received. If Parity Check function is not enabled (UPM[1]=0), the PE bit is always read zero.

11.9.7.3 Parity Checker

If Parity Bit is enabled (UPM[1]=1), the Parity Checker calculates the parity of the data bits in

incoming frame and compares the result with the parity bit from the received serial frame.

11.9.7.4 Disabling Receiver

In contrast to Transmitter, disabling the Receiver by clearing RXE bit makes the Receiver inactive

immediately. When the Receiver is disabled the Receiver flushes the receive buffer and the remaining

data in the buffer is all reset. The RXD pin is not overridden the function of UART, so RXD pin

becomes normal GPIO or primary function pin.

11.9.7.5 Asynchronous Data Reception

To receive asynchronous data frame, the UART includes a clock and data recovery unit. The Clock

Recovery logic is used for synchronizing the internally generated baud-rate clock to the incoming

asynchronous serial frame on the RXD pin.

The Data recovery logic samples and low pass filters the incoming bits, and this removes the noise of

RXD pin.

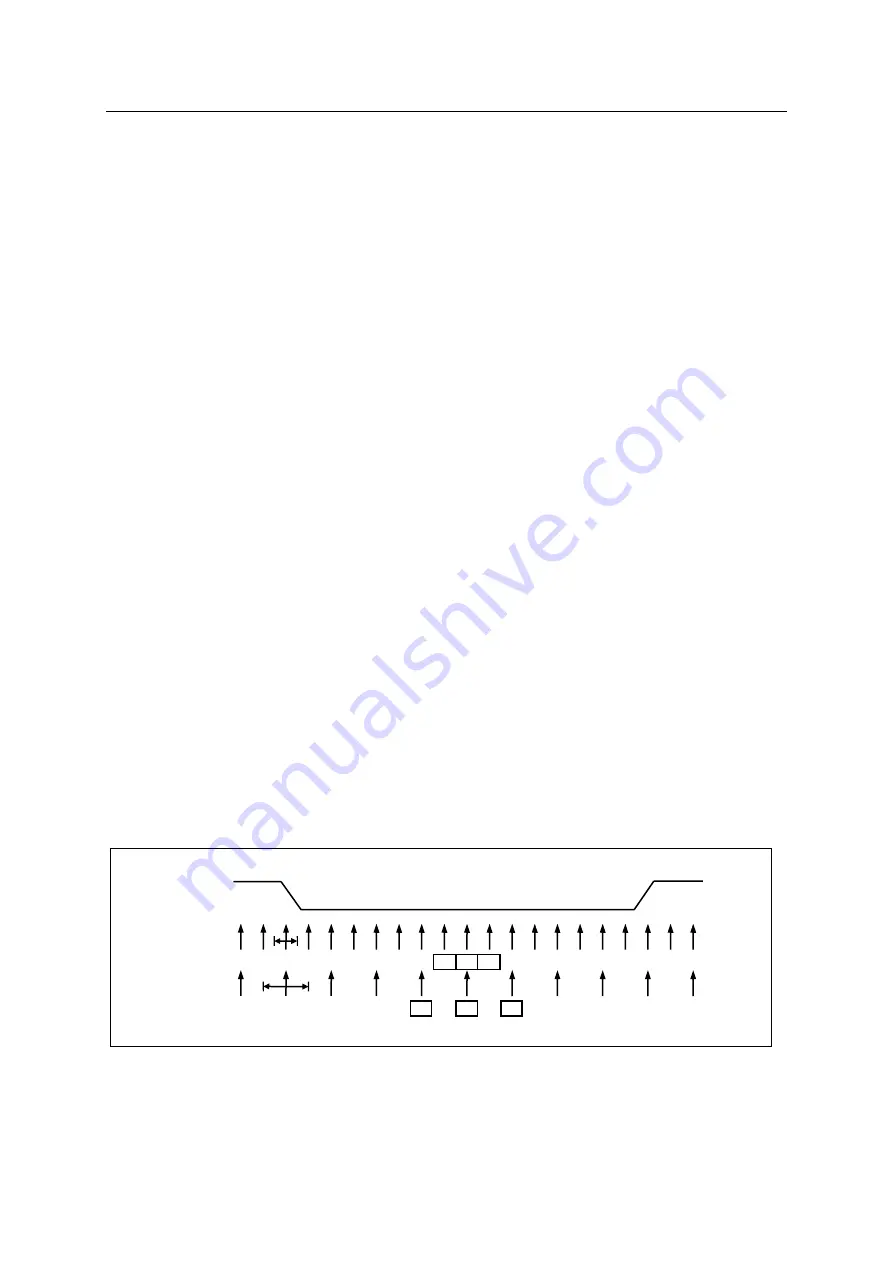

The next figure illustrates the sampling process of the start bit of an incoming frame. The sampling

rate is 16 times the baud-rate for normal mode, and 8 times the baud rate for Double Speed mode

(U2X=1). The horizontal arrows show the synchronization variation due to the asynchronous sampling

process. Note that larger time variation is shown when using the Double Speed mode.

When the Receiver is enabled (RXE=1), the clock recovery logic tries to find a high to low transition

on the RXD line, the start bit condition. After detecting high to low transition on RXD line, the clock

recovery logic uses samples 8,9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed

RXD

0

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

1

2

3

IDLE

BIT0

START

0

1

2

3

4

5

6

7

8

1

2

Sample

(U2X = 0)

Sample

(U2X = 1)

Figure 11-40 Start Bit Sampling