MC96FR116C

November, 2018 Rev.1.8

101

11.4.4.6 Register Map

Name

Address

Dir

Default

Description

T3CR2

C9

H

R/W

00

H

Timer 3 Mode Control Register 2

T3CR

CA

H

R/W

00

H

Timer 3 Mode Control Register

T3L

CB

H

R

00

H

Timer 3 Counter Low

PWM3DRL

CB

H

R/W

00

H

PWM 3 Duty Register Low

CDR3L

CB

H

R

00

H

Timer 3 Capture Data Register Low

T3H

CC

H

R

00

H

Timer 3 Counter High

PWM3DRH

CC

H

R/W

00

H

PWM 3 Duty Register High

CDR3H

CC

H

R

00

H

Timer 3 Capture Data Register High

T3DRL

CD

H

W

FF

H

Timer 3 Data Register Low

PWM3PRL

CD

H

W

FF

H

PWM 3 Period Register Low

T3DRH

CE

H

W

FF

H

Timer 3 Data Register High

PWM3PRH

CE

H

W

FF

H

PWM 3 Period Register High

Table 11-9 Register Map of Timer 3

11.4.4.7 Register Description

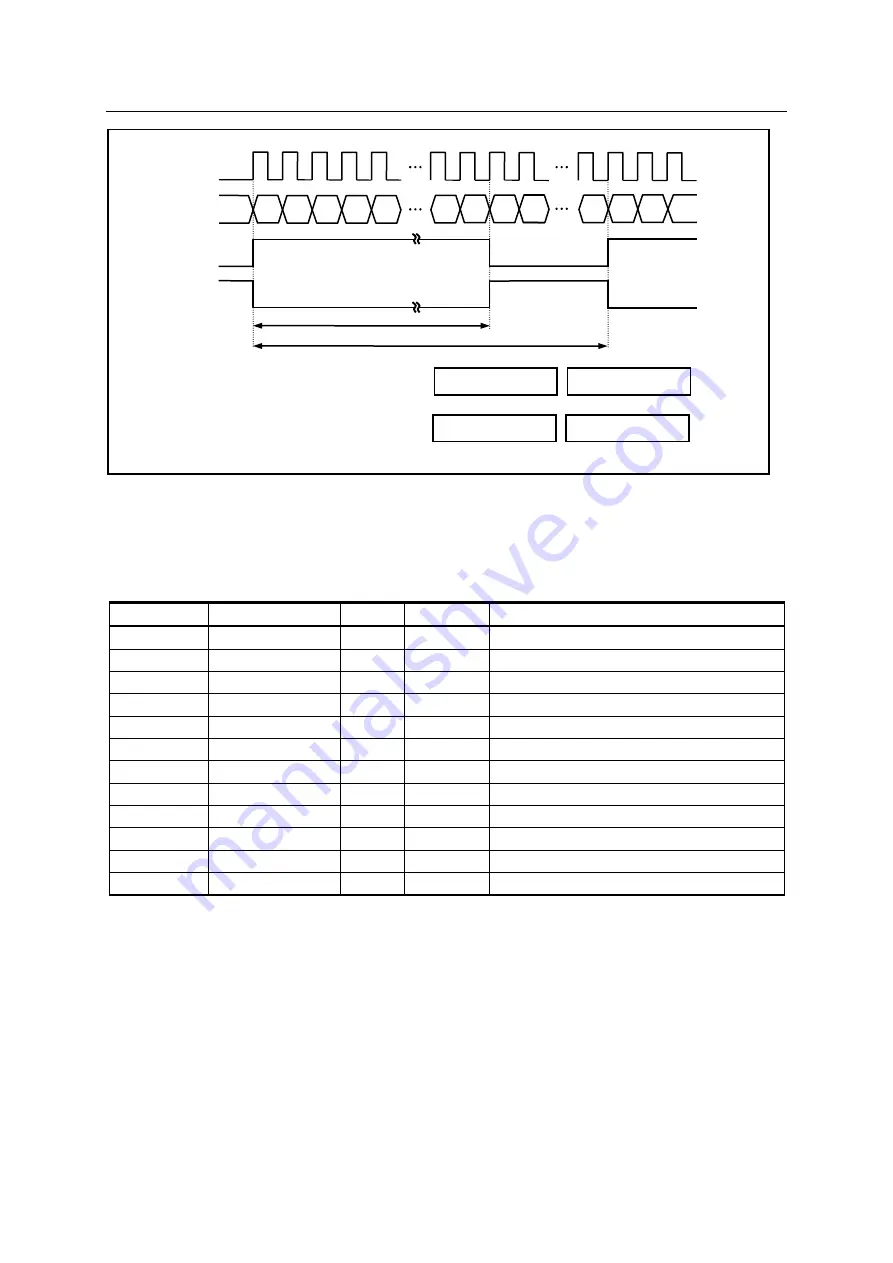

Timer3 can generate PWM output of 16-bit resolution. The period of PWM3 is decided by PWM3PRH

and PWM3PRL registers and the duty of PWM3 is decided by PWM3DRH and PWM3DRL registers.

PWM3PRH and PWM3PRL registers are write-only. Note that the value of period and duty registers

can be changed only when PWM3E bit in T3CR register is set.

CDR3H, PWM3DRH and T3H registers share peripheral address. When PWM mode is enabled,

reading this address gives PWM3DRH. When PWM mode is disabled, reading this address gives

CDR3H in Capture Mode or T3H in Output Compare Mode. Writing this address alters PWM3DRH

when PWM3E bit is

‘1’. When PWM mode is disabled, writing this address alters T3DRH.

Source Clock

(f

SCLK

)

Duty Cycle(1+0080

H

)X500ns = 64.50us

T3

00

01

02

03

04

7F

80

81

82

3FF

00

01

02

T3/PWM3

POL0 = 1

T3/PWM3

POL0 = 1

Period Cycle(1+03FF

H

)X500ns = 512us

1.95kHz

PWM3PRL(8-bit)

PWM3DRL(8-bit)

FF

H

80

H

T3CK[2:0] = 00

H

(f

SCLK

/2)

PWM3PRH = 03

H

PWM3PRL = FF

H

PWM3DRH = 00

H

PWM3DRL = 80

H

PWM3PRH(8-bit)

PWM3DRH(8-bit)

03

H

00

H

Figure 11-23 Example of PWM waveform (In case of f

SCLK

=4MHz)