Cache Controller

UG0331 User Guide Revision 15.0

136

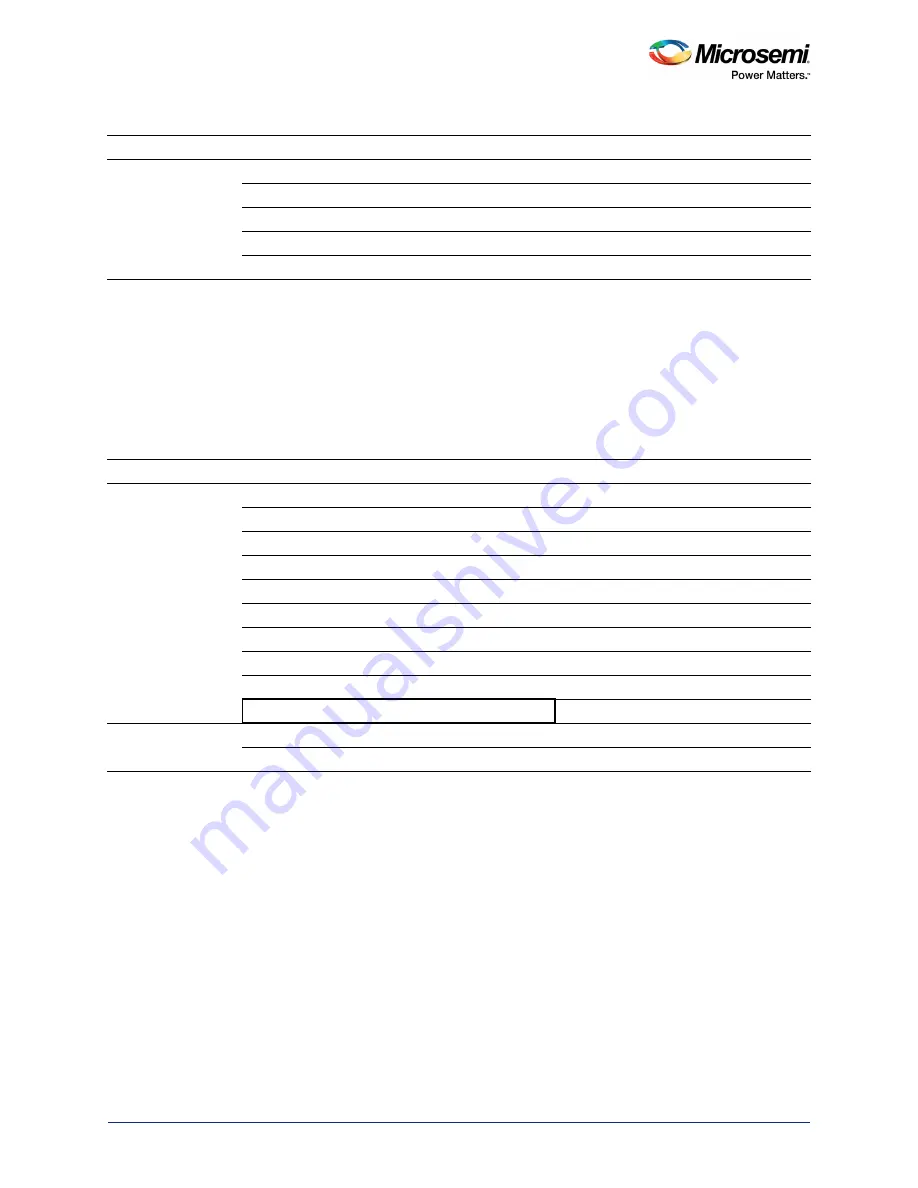

4.2.2.3

DDR Mapping

In DDR Remapping, the user boot code is present in the DDR. DDR remapping is also used for

debugging purposes. This can give high performance execution in systems where DDR is present. The

DDR is also used as the main memory for the Cache Controller. In case the of DDR remapping, the

cacheable region can be configured to 128 MB, 256 MB, or 512 MB. The Cache Controller generates the

appropriate DDR address as per remap configuration settings before putting the address on the MDDR

bridge.

4.2.3

Memory Maps and Transaction Mapping

The following table depicting transaction mapping depends upon the Memory map mode selected and

the possible destination slave for the transaction.

For example, the case eNVM Remapped mode is selected—the condition mentioned in the first row in

the table—If the cacheable transaction comes on ICode bus it will be targeted for the eNVM. This

transaction initiates on mirrored slave 2 (MS2). The transaction flow will be (MS4 – MM3 – MS2) and it

will be routed through AHB Bus Matrix. As shown in the

page 134, all the instruction fetch are

first checked in the Cache Engine that is MS4 and from there to Cache Memory. If not present, then as

shown in the following table, the corresponding routing slave will be selected (For eNVM Remap mode it

is switch MS2). The following are the abbreviations used in the table:

IC: Instruction CODE (ICODE) Cacheable

INC: ICODE Non Cacheable

NC: Non Cacheable

DC: Data CODE (DCODE) Cacheable

CM3 Code Region

DDR_SPACE 0 (256 MB)

0x1000_0000 to 0x1FFF_FFFF

Reserved

0x0018_0000 to 0x0FFF_FFFF

eNVM (Remap View) [512 KB]

0x0010_0000 to 0x0017_FFFF

Reserved

0x0001_0000 to 0x000F_FFFF

eSRAM0 & eSRAM1 [64 KB]

0x0000_0000 to 0x0000_FFFF

Table 90 •

DDR Remap

Data/Code Region

Space

Address

CM3 Data Region

Reserved

0xE000_0000 to 0xFFFF_FFFF

DDR _SPACE 3 (256 MB)

0xD000_0000 to 0xDFFF_FFFF

DDR _SPACE 2 (256 MB)

0xC000_0000 to 0xCFFF_FFFF

DDR _SPACE 1 (256 MB)

0xB000_0000 to 0xBFFF_FFFF

DDR _SPACE 0 (256 MB)

0xA000_0000 to 0xAFFF_FFFF

eNVM, Remap Area etc (1 GB)

0x6000_0000 to 0x9FFF_FFFF

Peripheral [SPI, UART, CAN, Fabric etc.] (0.5 GB) 0x4000_0000 to 0x5FFF_FFFF

Reserved

0x2001_0000 to 0x3FFF_FFFF

eSRAM-1 (32 KB)

0x2000_8000 to 0x2000_FFFF

eSRAM-0 (32 KB)

0x2000_0000 to 0x2000_7FFF

CM3 Code Region

DDR_SPACE 1 (256 MB)

0x1000_0000 to 0x1FFF_FFFF

DDR_SPACE 0 (256 MB)

0x0000_0000 to 0x0FFF_FFFF

Table 89 •

eSRAM Remapped Mode (Memory Map)

(continued)

Data/Code Region

Space

Address

Содержание SmartFusion2 MSS

Страница 1: ...UG0331 User Guide SmartFusion2 Microcontroller Subsystem ...

Страница 166: ...Cortex M3 Processor Reference Material UG0331 User Guide Revision 15 0 132 ...

Страница 200: ...Embedded NVM eNVM Controllers UG0331 User Guide Revision 15 0 166 Figure 87 System Builder Window ...

Страница 407: ...Universal Serial Bus OTG Controller UG0331 User Guide Revision 15 0 373 ...

Страница 806: ...Fabric Interface Controller UG0331 User Guide Revision 15 0 772 Figure 345 FIC Master AHB Lite Subsystem ...