CHAPTER 6 16-BIT TIMER/EVENT COUNTER 00

Preliminary User’s Manual U19014EJ1V0UD

167

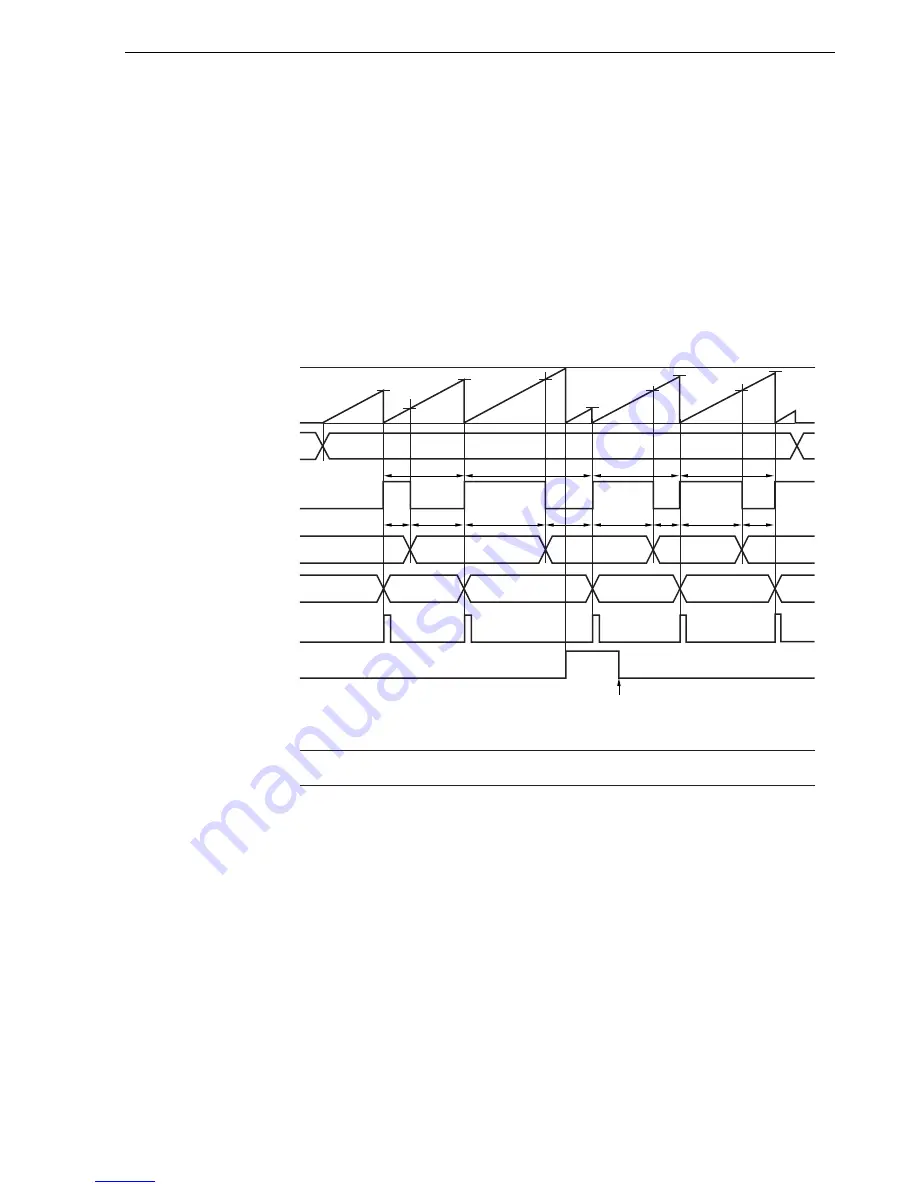

(3) Measuring the pulse width by using one input signal of the TI000 pin (clear & start mode entered by the

TI000 pin valid edge input)

Set the clear & start mode entered by the TI000 pin valid edge (TMC003 and TMC002 = 10). The count value of

TM00 is captured to CR000 in the phase reverse to the valid edge of the TI000 pin, and the count value of TM00

is captured to CR010 and TM00 is cleared (0000H) when the valid edge of the TI000 pin is detected. Therefore,

a cycle is stored in CR010 if TM00 does not overflow.

If an overflow occurs, take the value that results from adding 10000H to the value stored in CR010 as a cycle.

Clear bit 0 (OVF00) of 16-bit timer mode control register 00 (TMC00) to 0.

Figure 6-50. Timing Example of Pulse Width Measurement (3)

•

TMC00 = 08H, PRM00 = 10H, CRC00 = 07H

FFFFH

TM00 register

0000H

Operable bits

(TMC003, TMC002)

Capture & count clear input

(TI000)

Capture register

(CR000)

Capture register

(CR010)

Capture interrupt

(INTTM010)

Overflow flag

(OVF00)

Capture trigger input

(TI010)

Capture interrupt

(INTTM000)

10

<1>

<2>

<3>

<3>

<3>

<3>

<2>

<2>

<2>

<1>

<1>

<1>

M

A

B

C

D

N

S

P

Q

00

00

0 write clear

0000H

L

L

A

B

C

D

0000H

M

N

S

P

Q

<1> Pulse cycle =

(10000H

×

Number of times OVF00 bit is set to 1 + Captured value of CR010)

×

Count clock cycle

<2> High-level pulse width = (10000H

×

Number of times OVF00 bit is set to 1 + Captured value of CR000)

×

Count clock cycle

<3> Low-level pulse width = (Pulse cycle

−

High-level pulse width)

electronic components distributor