8-11

SYSTEM BUS DESIGN

Host snoop strobe (HSSTRB#) is an output signal which is driven by the EBC during any write

cycle on the host bus. It is asserted during I/O to memory DMA cycles, EISA/ISA bus master

write cycles to memory, and CPU write cycles to host memory.

8.3.4

EISA/ISA Bus Interface to the EBC

The EBC translates cycles from EISA masters that can be handled by ISA slaves and translates

cycles between ISA masters that can be handled by EISA slaves. It also facilitates transfers be-

tween 32-bit and 16-bit EISA devices and 16-bit and 8-bit ISA devices.

Most of the EISA and ISA bus signals connect directly to the EBC or ISP without buffers. The

direct connection assumes a worst case load of 300 pF and an IOL of 24 mA, with a worst case

clock-to-output propagation delay of 30 ns. Only the AEN8 control signal lacks a direct connec-

tion to EISA/ISA. AENx is a slot-specific signal that is decoded and asserted for a specific slot

of a particular address. The ISP unit provides a global AEN# that is decoded with the LA bus ad-

dress bit to generate the AENx signals. This is shown in

Table 8-1

.

The following is a brief functional description of the interface signals between the EISA/ ISA bus

and the EBC.

8.3.4.1

EBC and EISA Bus Interface Signals

Byte enables (BE3#–BE0#) are bidirectional signals that indicate which bytes are involved in the

current cycle. They are outputs during host bus master cycles and are inputs during ISA bus mas-

ter cycles. They are inputs during EISA bus master cycles and when the ISP is performing DMA

or refresh cycles.

Memory or I/O cycle (M/IO#) is an output signal that distinguishes between memory and I/O

EISA cycles. It is an output during ISA master cycles and during host bus master-to-EISA/ISA

slaves cycles. The signal floats during CPU, DMA, or EISA bus master cycles.

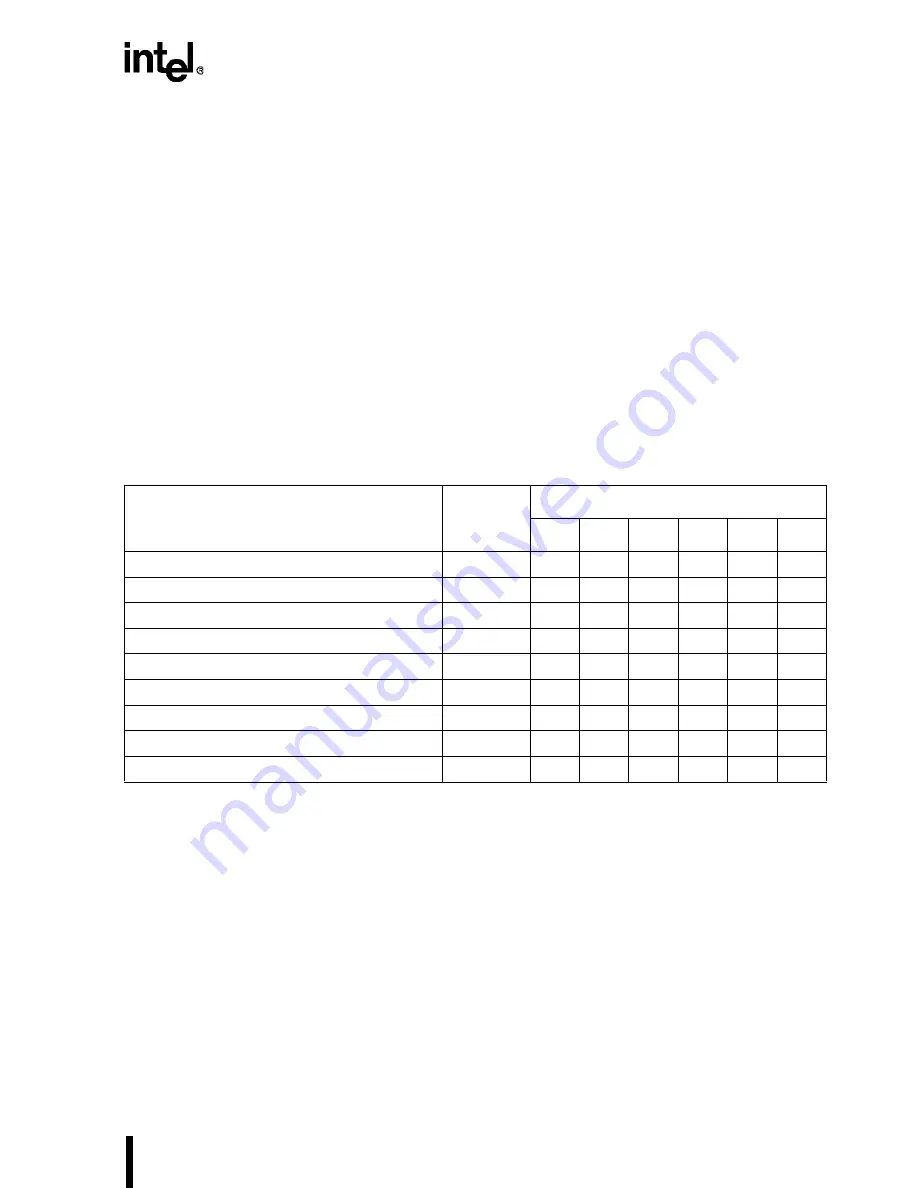

Table 8-1. AENx Decode Table

Address

AEN#

AENx

1

2

3

4

5

6

xxxx

1

1

1

1

1

1

1

00xx, 04xx, 08xx, 0Cxx

0

1

1

1

1

1

1

01xx--03xx, 05xx-07xx, 09xx-0Bxx, 0Dxx-0Fxx

0

0

0

0

0

0

0

10xx, 14xx, 18xx, 1Cxx

0

0

1

1

1

1

1

20xx, 24xx, 28xx, 2Cxx

0

1

0

1

1

1

1

30xx, 34xx, 38xx, 3Cxx

0

1

1

0

1

1

1

40xx, 44xx, 48xx, 4Cxx

0

1

1

1

0

1

1

50xx, 54xx, 58xx, 5Cxx

0

1

1

1

1

0

1

60xx, 64xx, 68xx, 6Cxx

0

1

1

1

1

1

0

Summary of Contents for Embedded Intel486

Page 16: ......

Page 18: ......

Page 26: ......

Page 28: ......

Page 42: ......

Page 44: ......

Page 62: ......

Page 64: ......

Page 138: ......

Page 140: ......

Page 148: ......

Page 150: ......

Page 170: ......

Page 172: ......

Page 226: ......

Page 228: ......

Page 264: ......

Page 282: ......

Page 284: ......