EMBEDDED Intel486™ PROCESSOR HARDWARE REFERENCE MANUAL

4-44

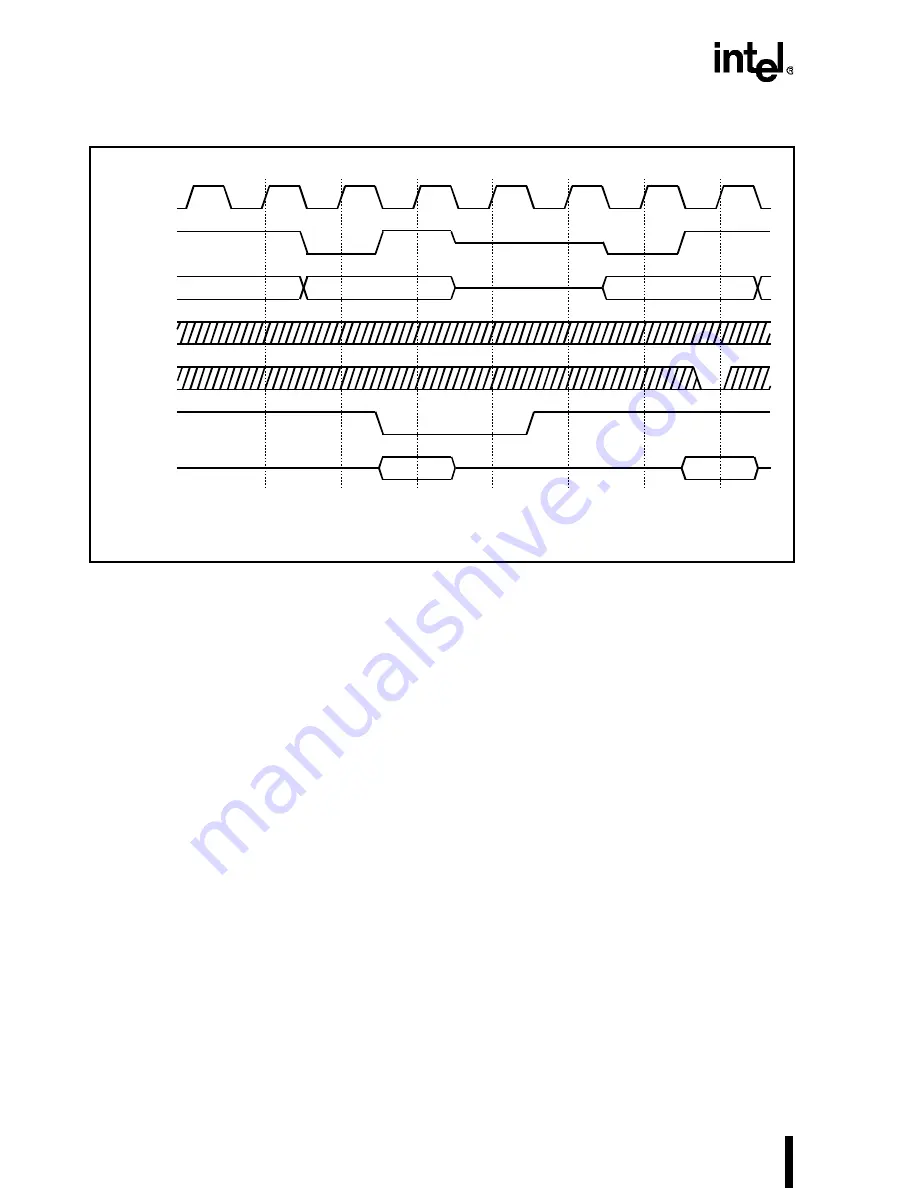

Figure 4-34. Restarted Write Cycle

The device asserting BOFF# is free to run cycles while the Intel486 processor bus is in its high

impedance state. If backoff is requested after the Intel486 processor has started a cycle, the new

master should wait for memory to assert RDY# or BRDY# before assuming control of the bus.

Waiting for RDY# or BRDY# provides a handshake to ensure that the memory system is ready

to accept a new cycle. If the bus is idle when BOFF# is asserted, the new master can start its cycle

two clocks after issuing BOFF#.

The external memory can view BOFF# in the same manner as BLAST#. Asserting BOFF# tells

the external memory system that the current cycle is the last cycle in a transfer.

The bus remains in the high impedance state until BOFF# is deasserted. Upon negation, the

Intel486 processor restarts its bus cycle by driving out the address and status and asserting ADS#.

The bus cycle then continues as usual.

Asserting BOFF# during a burst, BS8#, or BS16# cycle forces the Intel486 processor to ignore

data returned for that cycle only. Data from previous cycles is still valid. For example, if BOFF#

is asserted on the third BRDY# of a burst, the Intel486 processor assumes the data returned with

the first and second BRDY# is correct and restarts the burst beginning with the third item. The

same rule applies to transfers broken into multiple cycles by BS8# or BS16#.

Asserting BOFF# in the same clock as ADS# causes the Intel486 processor to float its bus in the

next clock and leave ADS# floating low. Because ADS# is floating low, a peripheral may think

that a new bus cycle has begun even though the cycle was aborted. There are two possible solu-

tions to this problem. The first is to have all devices recognize this condition and ignore ADS#

until RDY# is asserted. The second approach is to use a “two clock” backoff: in the first clock

242202-147

CLK

ADS#

ADDR

SPEC

BRDY#

DATA

Ti

T1

T2

Ti

From Processor

‡

Tb

Tb

T1b

T2

BOFF#

RDY#

100

100

‡

‡

Summary of Contents for Embedded Intel486

Page 16: ......

Page 18: ......

Page 26: ......

Page 28: ......

Page 42: ......

Page 44: ......

Page 62: ......

Page 64: ......

Page 138: ......

Page 140: ......

Page 148: ......

Page 150: ......

Page 170: ......

Page 172: ......

Page 226: ......

Page 228: ......

Page 264: ......

Page 282: ......

Page 284: ......