543

CHAPTER 24 512K-BIT FLASH MEMORY

24.6.3

Timing Limit Exceeded Flag (DQ5)

The timing limit exceeded flag (DQ5) is used to post that execution of the automatic

algorithm has exceeded the time (internal pulse count) prescribed in the flash memory.

■

Timing Limit Exceeded Flag (DQ5)

Table 24.6-7 and Table 24.6-8 list the state transitions of the timing limit exceeded flag.

●

Write/chip erase

Read-access after write or chip erase automatic algorithm activation causes the flash memory to output 0 if

the time is within the prescribed time (time required for write/erase) or to output 1 if the prescribed time

has been exceeded. Because this is done regardless of whether the automatic algorithm is being executed or

has terminated, it is possible to determine whether write/erase was successful or unsuccessful. That is,

when this flag outputs 1, writing can be determined to have been unsuccessful if the automatic algorithm is

still being executed by the data polling function or toggle bit function.

For example, writing 1 to a flash memory address where 0 has been written will cause the fail state to

occur. In this case, the flash memory will lock and execution of the automatic algorithm will not terminate.

In rare cases normal termination may be seen as with the case where "1" can be written. As a result, valid

data will not be outputted from the data polling flag (DQ7). In addition, the toggle bit flag (DQ6) will

exceed the time limit without stopping the toggle operation and the timing limit exceeded flag (DQ5) will

output 1. Note that this state indicates that the flash memory is not faulty, but has not been used correctly.

When this state occurs, execute the Reset command.

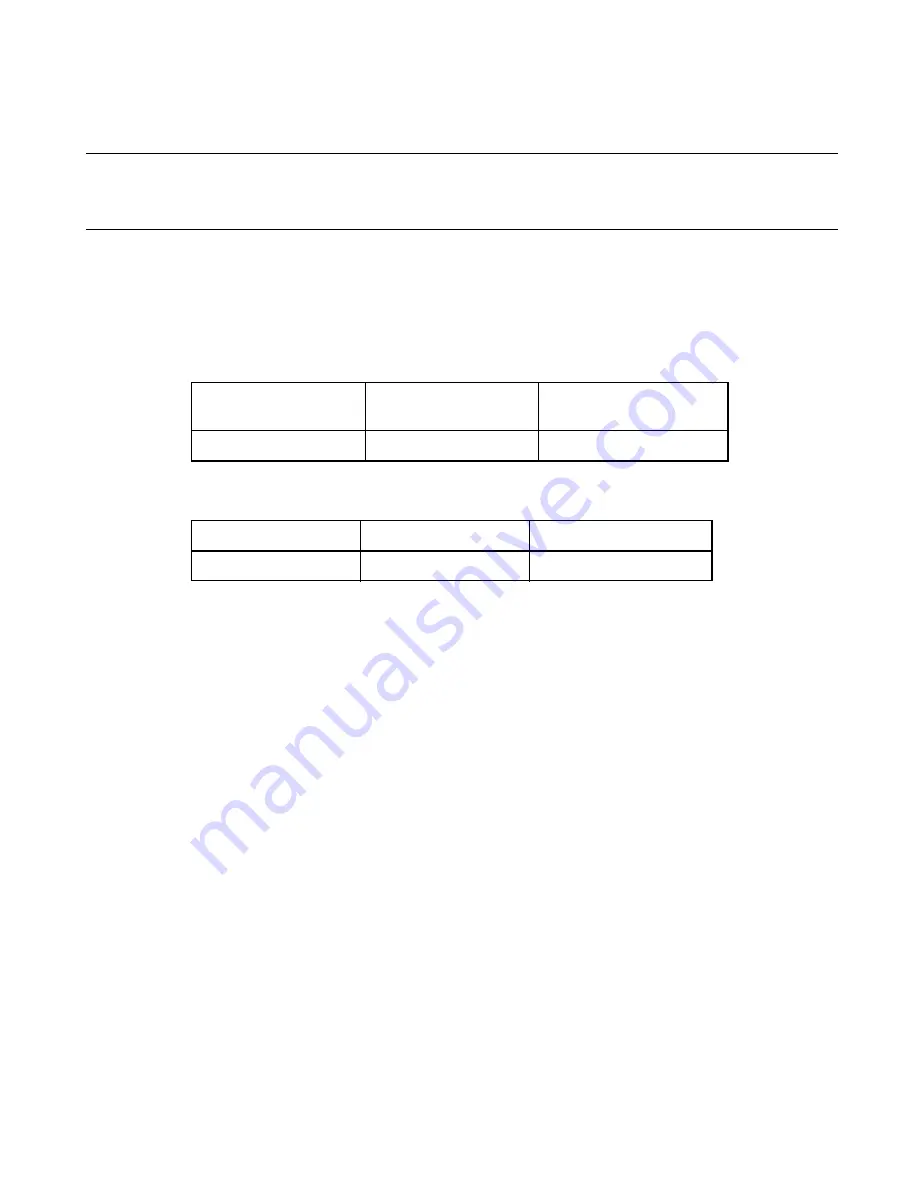

Table 24.6-7 State Transition of Timing Limit Exceeded Flag (State change at normal

operation)

Operating State

Programming

→

Completed

Chip Erasing

→

Completed

DQ5 0

→

DATA:5

0

→

1

Table 24.6-8 State Transition of Timing Limit Exceeded Flag (State change at abnormal

operation)

Operating State

Programming

Chip Erasing

DQ5 1

1

Summary of Contents for F2MCTM-16LX

Page 2: ......

Page 3: ...FUJITSU LIMITED F2MCTM 16LX 16 BIT MICROCONTROLLER MB90360 Series HARDWARE MANUAL ...

Page 4: ......

Page 42: ...26 CHAPTER 1 OVERVIEW ...

Page 70: ...54 CHAPTER 2 CPU ...

Page 134: ...118 CHAPTER 6 CLOCK SUPERVISOR ...

Page 176: ...160 CHAPTER 8 LOW POWER CONSUMPTION MODE ...

Page 194: ...178 CHAPTER 10 I O PORTS ...

Page 252: ...236 CHAPTER 13 16 Bit I O TIMER ...

Page 282: ...266 CHAPTER 14 16 BIT RELOAD TIMER ...

Page 296: ...280 CHAPTER 15 WATCH TIMER ...

Page 386: ...370 CHAPTER 18 8 10 BIT A D CONVERTER ...

Page 426: ...410 CHAPTER 20 LIN UART Figure 20 5 2 ORE Flag Set Timing RDRF ORE Reception data ...

Page 540: ...524 CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION ...

Page 568: ...552 CHAPTER 24 512K BIT FLASH MEMORY ...

Page 633: ...617 APPENDIX B Instructions Table B 9 3 Bit Operation Instruction Map first byte 6CH ...

Page 634: ...618 APPENDIX Table B 9 4 Character String Operation Instruction Map first byte 6EH ...

Page 637: ...621 APPENDIX B Instructions Table B 9 7 ea Instruction 2 first byte 71H ...

Page 638: ...622 APPENDIX Table B 9 8 ea Instruction 3 first byte 72H ...

Page 639: ...623 APPENDIX B Instructions Table B 9 9 ea Instruction 4 first byte 73H ...

Page 640: ...624 APPENDIX Table B 9 10 ea Instruction 5 first byte 74H ...

Page 641: ...625 APPENDIX B Instructions Table B 9 11 ea Instruction 6 first byte 75H ...

Page 642: ...626 APPENDIX Table B 9 12 ea Instruction 7 first byte 76H ...

Page 643: ...627 APPENDIX B Instructions Table B 9 13 ea Instruction 8 first byte 77H ...

Page 644: ...628 APPENDIX Table B 9 14 ea Instruction 9 first byte 78H ...

Page 645: ...629 APPENDIX B Instructions Table B 9 15 MOVEA RWi ea Instruction first byte 79H ...

Page 646: ...630 APPENDIX Table B 9 16 MOV Ri ea Instruction first byte 7AH ...

Page 647: ...631 APPENDIX B Instructions Table B 9 17 MOVW RWi ea Instruction first byte 7BH ...

Page 648: ...632 APPENDIX Table B 9 18 MOV Ri ea Instruction first byte 7CH ...

Page 649: ...633 APPENDIX B Instructions Table B 9 19 MOVW ea Rwi Instruction first byte 7DH ...

Page 650: ...634 APPENDIX Table B 9 20 XCH Ri ea Instruction first byte 7EH ...

Page 651: ...635 APPENDIX B Instructions Table B 9 21 XCHW RWi ea Instruction first byte 7FH ...

Page 664: ...648 APPENDIX ...

Page 665: ...649 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Page 682: ......