429

CHAPTER 20 LIN-UART

20.7.3

Operation with LIN Function (Operation Mode 3)

LIN-UART can be used either as LIN-Master or LIN-Slave. For this LIN function a special

mode is provided. Setting the LIN-UART to mode 3 configures the data format to 8N1-

LSB-first format.

■

Operation in Asynchronous LIN Mode (Operation mode 3)

●

LIN-UART as LIN master

In LIN master mode, the master determines the baud rate of the whole bus, therefore slaves devices have to

synchronize to the master. Therefore, the desired baud rate remains fixed in master operation after

initialization.

Writing a "1" into the LBR bit of the Extended Communication Control Register (ECCR) generates a 13 -

16 bit time low-level on the SOTn pin, which is the LIN synchronization break and the start of a LIN

message. Thereby the TDRE flag of the Serial Status Register (SSR) goes "0" and is reset to "1" after the

break, and generates a transmission interrupt for the CPU (if TIE of SSR is "1").

The length of the LIN break to be sent can be determined by the LBL1/0 bits of the ESCR as follows:

The Synch Field is sent as byte data of 0x55 after the LIN break. To prevent a transmission interrupt, the

0x55 can be written to the TDR just after writing the "1" to the LBR bit, although the TDRE flag is "0".

●

LIN-UART as LIN slave

In LIN slave mode, LIN-UART has to synchronize to the master’s baud rate. If Reception is disabled (RXE

= 0) but LIN break interrupt is enabled (LBIE = 1) LIN-UART will generate a reception interrupt, if a

synchronization break from the LIN master is detected, and indicates it with the LBD flag of the ESCR to

"1". Writing "0" to this bit clears the reception interrupt request. For the calculation of the baud rate, the

UART0 operation is explained as an example. When UART0 detects first falling edge of synch field, set

the internal signal inputted to the input capture (ICU0) to "H" and start ICU0. This internal signal is set to

"L" at fifth falling edge, ICU0 must be set to the LIN mode (ICE01). Also, the ICUO interrupt must be set

to enable and to detect both edges (ICS01).

The time when the ICU0 input signal is "1" is the value in which eight baud rates are multiplied. Therefore,

baud rate setting value is summarized as follows:

without free-run timer overflow : BGR value = (b-a)/8 -1

with free-run timer overflow : BGR value = (Max + b-a)/8-1

where Max is the free-run timer maximum value at the overflow occurs.

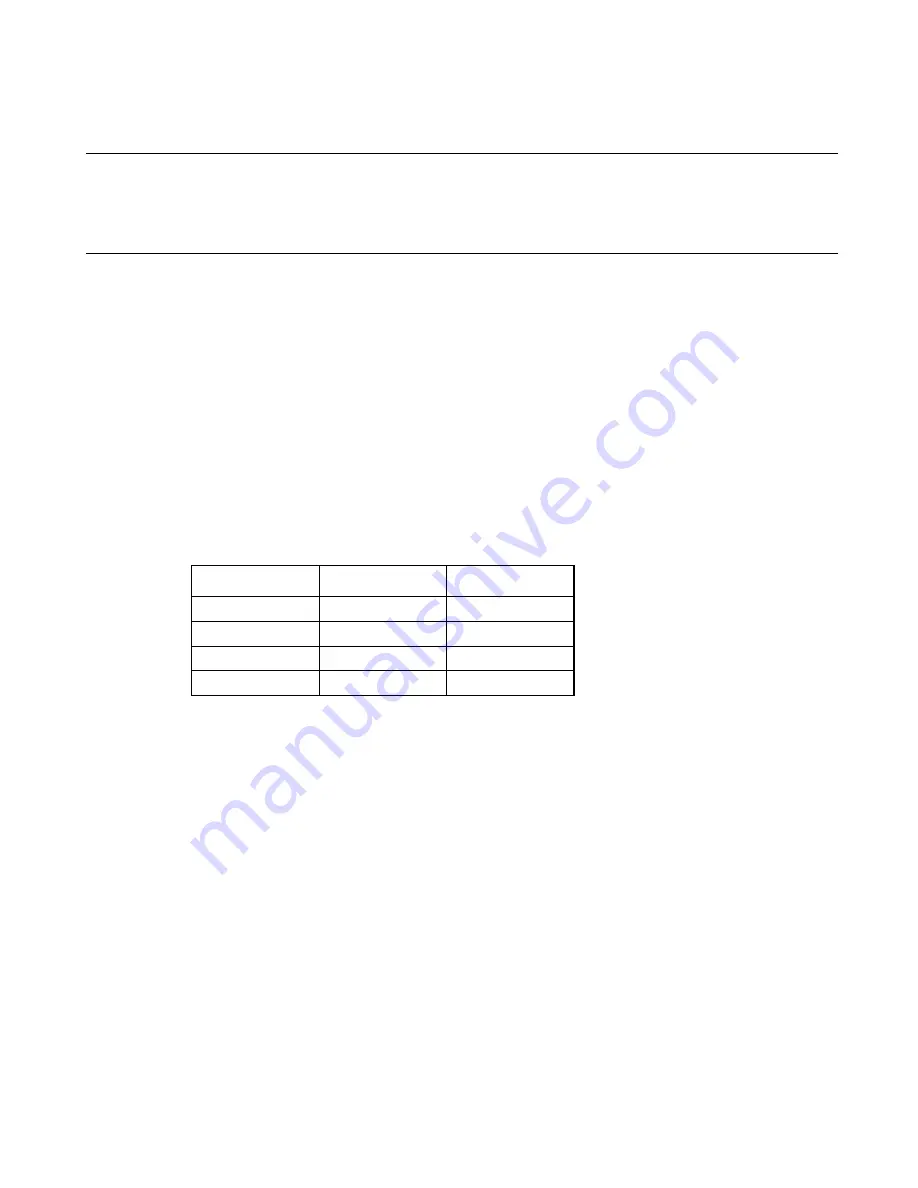

Table 20.7-2 LIN Break Length

LBL0

LBL1

Break length

0

0

13 bits

1

0

14 bits

0

1

15 bits

1

1

16 bits

Summary of Contents for F2MCTM-16LX

Page 2: ......

Page 3: ...FUJITSU LIMITED F2MCTM 16LX 16 BIT MICROCONTROLLER MB90360 Series HARDWARE MANUAL ...

Page 4: ......

Page 42: ...26 CHAPTER 1 OVERVIEW ...

Page 70: ...54 CHAPTER 2 CPU ...

Page 134: ...118 CHAPTER 6 CLOCK SUPERVISOR ...

Page 176: ...160 CHAPTER 8 LOW POWER CONSUMPTION MODE ...

Page 194: ...178 CHAPTER 10 I O PORTS ...

Page 252: ...236 CHAPTER 13 16 Bit I O TIMER ...

Page 282: ...266 CHAPTER 14 16 BIT RELOAD TIMER ...

Page 296: ...280 CHAPTER 15 WATCH TIMER ...

Page 386: ...370 CHAPTER 18 8 10 BIT A D CONVERTER ...

Page 426: ...410 CHAPTER 20 LIN UART Figure 20 5 2 ORE Flag Set Timing RDRF ORE Reception data ...

Page 540: ...524 CHAPTER 22 ADDRESS MATCH DETECTION FUNCTION ...

Page 568: ...552 CHAPTER 24 512K BIT FLASH MEMORY ...

Page 633: ...617 APPENDIX B Instructions Table B 9 3 Bit Operation Instruction Map first byte 6CH ...

Page 634: ...618 APPENDIX Table B 9 4 Character String Operation Instruction Map first byte 6EH ...

Page 637: ...621 APPENDIX B Instructions Table B 9 7 ea Instruction 2 first byte 71H ...

Page 638: ...622 APPENDIX Table B 9 8 ea Instruction 3 first byte 72H ...

Page 639: ...623 APPENDIX B Instructions Table B 9 9 ea Instruction 4 first byte 73H ...

Page 640: ...624 APPENDIX Table B 9 10 ea Instruction 5 first byte 74H ...

Page 641: ...625 APPENDIX B Instructions Table B 9 11 ea Instruction 6 first byte 75H ...

Page 642: ...626 APPENDIX Table B 9 12 ea Instruction 7 first byte 76H ...

Page 643: ...627 APPENDIX B Instructions Table B 9 13 ea Instruction 8 first byte 77H ...

Page 644: ...628 APPENDIX Table B 9 14 ea Instruction 9 first byte 78H ...

Page 645: ...629 APPENDIX B Instructions Table B 9 15 MOVEA RWi ea Instruction first byte 79H ...

Page 646: ...630 APPENDIX Table B 9 16 MOV Ri ea Instruction first byte 7AH ...

Page 647: ...631 APPENDIX B Instructions Table B 9 17 MOVW RWi ea Instruction first byte 7BH ...

Page 648: ...632 APPENDIX Table B 9 18 MOV Ri ea Instruction first byte 7CH ...

Page 649: ...633 APPENDIX B Instructions Table B 9 19 MOVW ea Rwi Instruction first byte 7DH ...

Page 650: ...634 APPENDIX Table B 9 20 XCH Ri ea Instruction first byte 7EH ...

Page 651: ...635 APPENDIX B Instructions Table B 9 21 XCHW RWi ea Instruction first byte 7FH ...

Page 664: ...648 APPENDIX ...

Page 665: ...649 INDEX INDEX The index follows on the next page This is listed in alphabetic order ...

Page 682: ......