SMARC T335x Carrier Board Hardware Design Guide, Document Revision 1.2

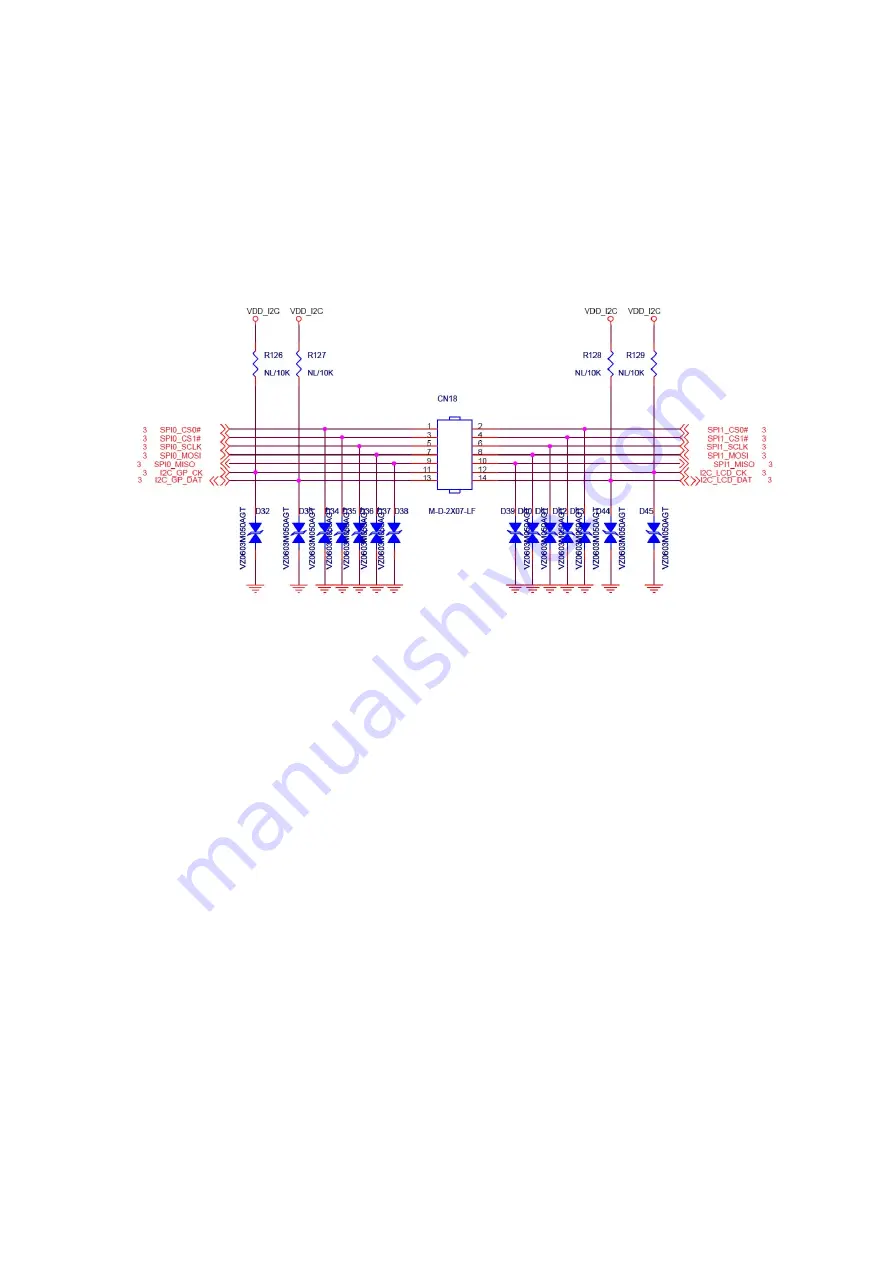

2.9.3. SPI Implementation Reference Schematic

The example shown below is implemented on the

SMARC T335X

evaluation

carrier board. SPI signals are presented in a 2.0mm header. A varistor is

applied on each signal line and able to withstand

ESD

test of IEC-61000-4-2

and surge protection.

Figure 33: SPI Signals Reference Schematic

2.9.4. Unused SPI Signals Termination

All unused SPI signals can be left unconnected.