SMARC T335x Carrier Board Hardware Design Guide, Document Revision 1.2

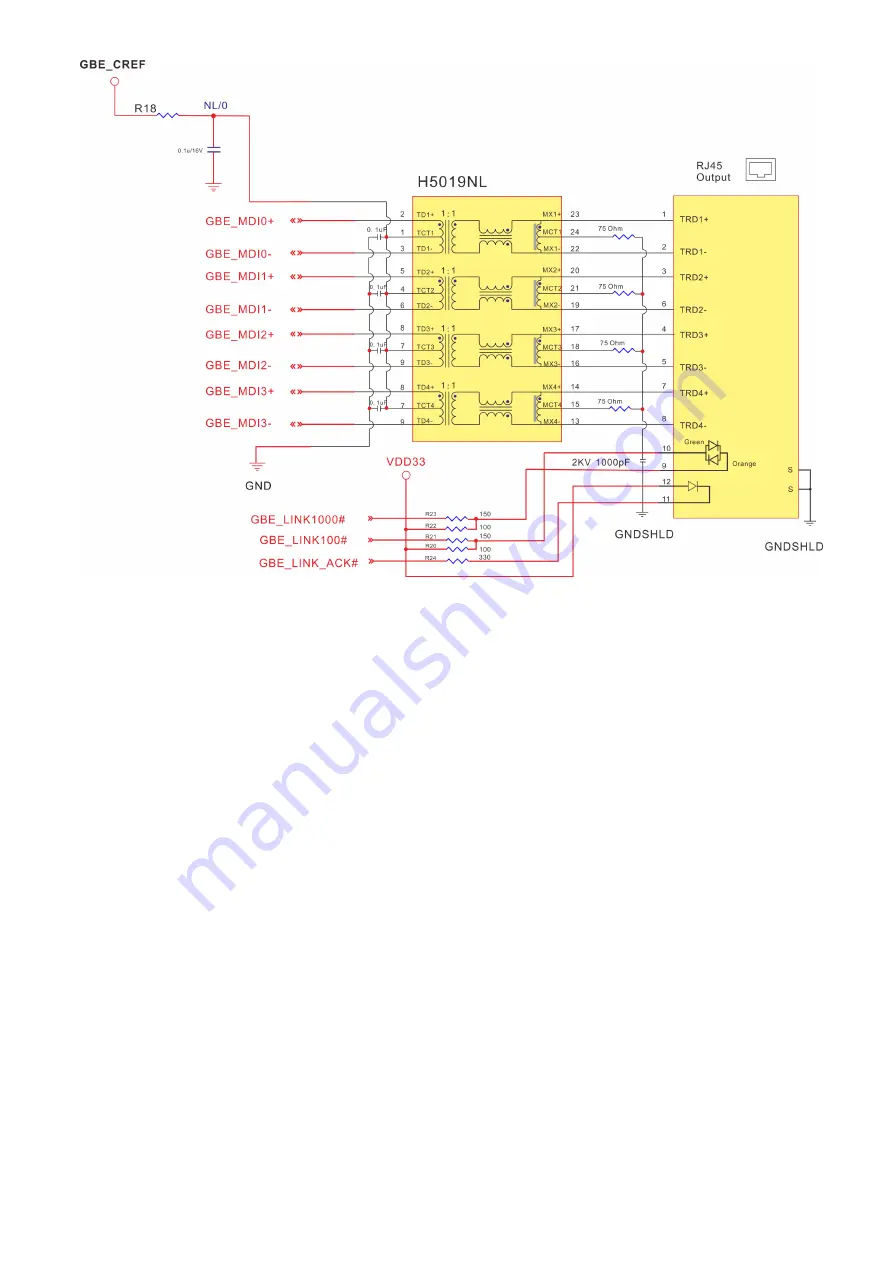

Figure 10: Gigabit Ethernet with Discrete Magnetics Reference

Schematic

2.2.3.3. 10/100Mbit Ethernet Schematic Example (Integrated

Magnetics)

The Fast Ethernet interface uses the

MDI0

as transmitting lanes and the

MDI1

as receiving lane. As most Ethernet

PHYs

feature Auto-MDIX, the

signal direction RX and TX could be swapped. It is strongly recommend

that RX and TX lanes are not swapped in order to ensure compatibility

between all

SMARC

modules.

The

MDI2

and

MDI3

lanes are not used for the

10/100Base-TX

interface.

These signals can be left unconnected.

Most of the Fast Ethernet

PHYs

do not need a centre tap voltage. Even so,

it is recommend the centre tap pins of the magnetics are connected to the

centre tap source pin of the

SMARC

module connector.