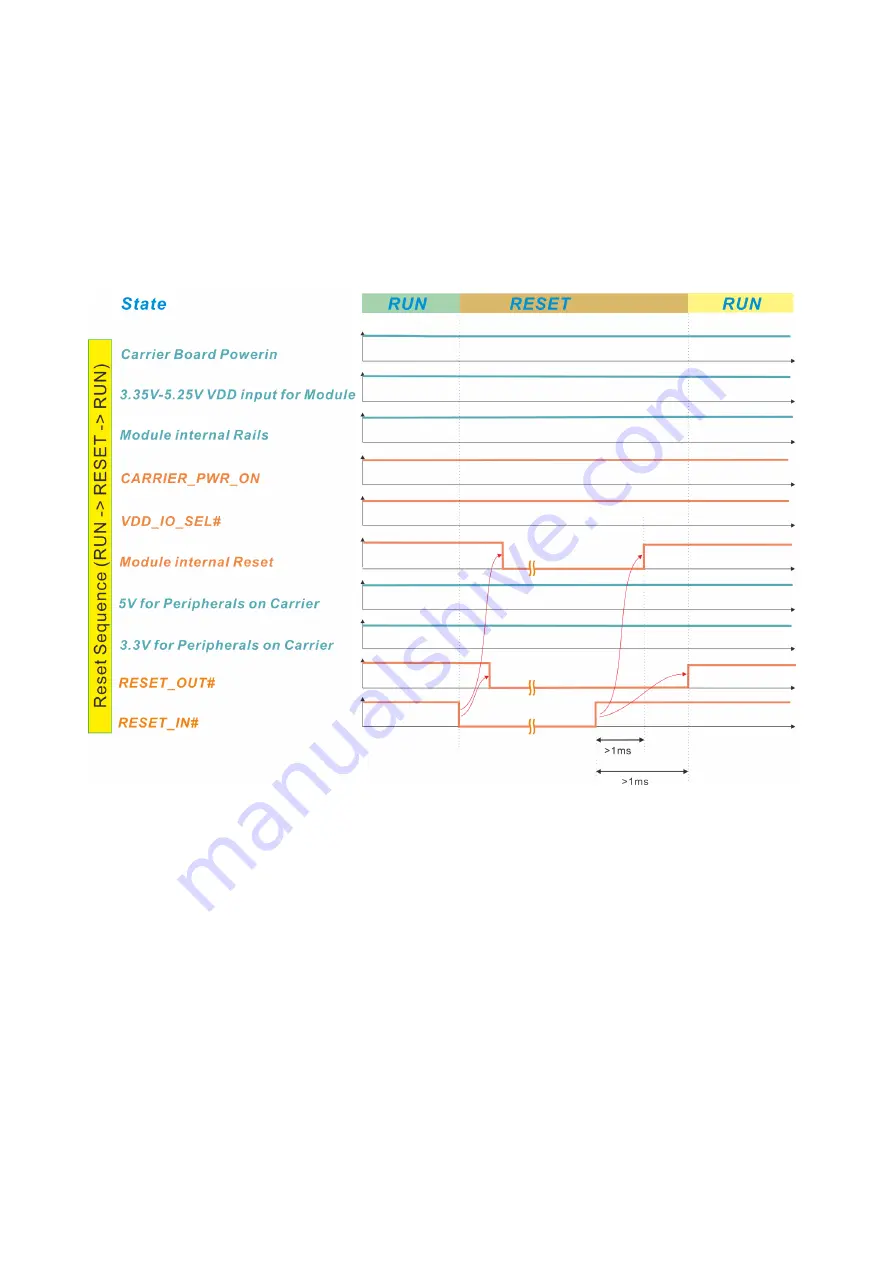

SMARC T335x Carrier Board Hardware Design Guide, Document Revision 1.2

When the

RESET_IN#

is asserted, a reset cycle is initiated. The module

internal reset and the external reset output

RESET_OUT#

are asserted as

long as

RESET_IN#

is asserted. If the reset input

RESET_IN#

is de-asserted,

the internal reset and the

RESET_OUT#

will remain low for at least 1ms until

they are also de-asserted and the module starts booting again. This

guarantees a minimum reset time of 1ms even if the reset input

RESET_IN#

is

triggered for a short time.

Figure 42: Reset Sequence