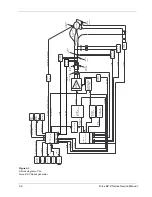

Control Board

Principles of Operation

Force EZ-C Series Service Manual

5-7

Shared RAM

An IDT 713425A device (U4) with semaphore flags provides the 4K x 8 external

shared static RAM. The shared RAM allows the main microcontroller (U5) and

the feedback microcontroller (U11) to share common variables. It functions as a

communications interface between the main and feedback microcontrollers. It

also provides these microcontrollers with additional general purpose RAM.

Real-Time Clock

The real-time clock (U1), a DS12885, tracks the date and time of day and

provides 128 bytes of battery-backed RAM. Of the 128 bytes, it uses 14 internal

to the chip for the clock and control registers. The main microcontroller uses 114

bytes of general purpose RAM to store calibration constants, special features

settings, and last setup parameters.

I/0 Expansion

Three devices provide I/O expansion capabilities:

•

One ST microelectronics PSD835G2 programmable systems device

•

One ST microelectronics PSD835G2 programmable systems device

•

82C55 expansion port (U2)

The ST Microelectronics PSD835G2 incorporates 52 individually programmable

I/O pins divided into 6 ports of 8-bits each and 1 port of 4-bits. Of the general I/O

pins, 24 can by alternatively utilized for 24 PLD outputs. The PSD835G2 also

contains 512K x 8 main flash memory, 32K x 8 boot flash memory, 2K x 8 of

SRAM, and a power management unit for battery backup. The power

management unit for battery backup is not used by the feedback microcontroller.

The I/O expansion capabilities of the feedback PSD835G2 has a built-in IEEE

1149.1 compliant JTAG serial port to allow full-chip in-system programmability

(ISP). The main PSD835G2 is #1 on the JTAG chain and the feedback

PSD835G2 with the exception that the 512K x 8 flash memory for the main

PSD835G2 is accessed in a bank switching methodology and the I/O expansion

capabilities are configured as outputs for lamp control, keyboard scanning, and

chip selects. The 82C55 is configured as all inputs, and is used to read the

keyboard, keying signals, accessory switches, and system status flags.

Keyboard Interface and Activation Inputs

The keyboard interface is a simple row and column matrix between three bank

select output lines (BANK0–BANK2) on port A of the PSD835G2 (U3) used by

the main microcontroller and eight keyboard (KBD_D0–KBD_D7) input lines on

port A of the 82C55 expansion port (U2).

Port B of the 82C55 expansion port reads activation inputs from the IsoBloc

decoding circuits on the Power Supply/RF board.

Содержание Force EZ - C Series

Страница 1: ...Service Manual Valleylab Force EZ C Series Electrosurgical Generator with Instant Response Technology...

Страница 6: ...vi Force EZ C Series Service Manual...

Страница 20: ...1 6 Force EZ C Service Manual...

Страница 64: ...4 30 Force EZ C Series Service Manual...

Страница 156: ...7 26 Force EZ C Series Service Manual...

Страница 158: ...Interconnect Diagram 8 2 Force EZ C Series Service Manual Interconnect Diagram Figure 8 1 Electric cable connections...

Страница 208: ...10 18 Force EZ C Series Service Manual...