Semiconductor Group

5-1

1997-10-01

Reset / System Clock

C541U

5

Reset and System Clock Operation

5.1

Hardware Reset Operation

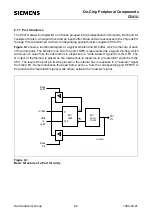

The hardware reset function incorporated in the C541U allows for an easy automatic start-up at a

minimum of additional hardware and forces the controller to a predefined default state. The

hardware reset function can also be used during normal operation in order to restart the device. This

is particularly done when the power down mode is to be terminated.

Additional to the hardware reset, which is applied externally to the device, there are two internal

reset sources, the watchdog timer and the oscillator watchdog. This chapter deals only with the

external hardware reset.

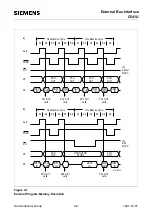

The RESET input is an active high input. An internal Schmitt trigger is used at the input for noise

rejection. Since the reset is synchronized internally, the RESET pin must be held high for at least

two machine cycles (12 oscillator periods) while the oscillator is running. With the oscillator running

the internal reset is executed during the second machine cycle and is repeated every cycle until

RESET goes low again.

During reset, pins ALE and PSEN are configured as inputs and should not be stimulated or driven

externally. (An external stimulation at these lines during reset activates several test modes which

are reserved for test purposes. This in turn may cause unpredictable output operations at several

port pins).

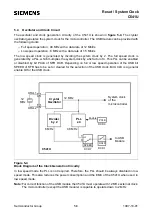

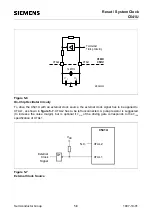

At the RESET pin, a pulldown resistor is internally connected to

V

SS

to allow a power-up reset with

an external capacitor only. An automatic power-up reset can be obtained when

V

DD

is applied by

connecting the RESET pin to

V

DD

via a capacitor. After

V

DD

has been turned on, the capacitor must

hold the voltage level at the reset pin for a specific time to effect a complete reset.

The time required for a reset operation is the oscillator start-up time plus 2 machine cycles, which,

under normal conditions, must be at least 10 - 20 ms for a crystal oscillator. This requirement is

typically met using a capacitor of 4.7 to 10

µ

F. The same considerations apply if the reset signal is

generated externally (figure 5-1 b). In each case it must be assured that the oscillator has started

up properly and that at least two machine cycles have passed before the reset signal goes inactive.

Содержание C541U

Страница 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Страница 7: ......

Страница 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Страница 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Страница 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Страница 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Страница 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...

Страница 192: ...Semiconductor Group 12 7 Index C541U ...