Semiconductor Group

6-76

1999-04-01

On-Chip Peripheral Components

C541U

6.4.8.2

Transfer Modes

According to the USB Specification Rev1.0 the low speed mode is only supported in control transfer

mode and interrupt transfer mode. The two supported transfer modes are described here.

There are times when the hardware is busy updating the registers and accesses to USBDRn

registers are blocked. Software has to wait until the TYPE bit field of USBDCR register is set to

0000

B

or ‘Empty’.

6.4.8.3

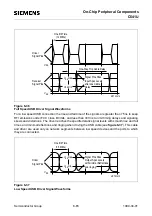

Control Transfer

Control transfer is always directed to/from the control endpoint, EP0. This type of transfer consists

of two or three stages. At the end of each stage an acknowledgement needs to be generated by

writing 0000

B

or ‘Empty’ to the TYPE bit field.

6.4.8.3.1 Setup Stage

The host always initiates this stage by sending a SETUP packet to the device. SETUP interrupt

request will be generated and the TYPE bit field of USBDCR contains 0010

B

or ‘SETUP packet’.

The data packet associated with this stage will be stored in the USBDRn registers, while the packet

length is recorded in the LEN bit field of USBDCR register.

Software is then required to read the registers in order to detect the transfer. The SETUP interrupt

request will be cleared by reading the USBDCR register. The stage is completed by writing ‘Empty’

to the TYPE bit field.

Since C541U only supports single device configuration and single interface, setting multiple device

configuration through “set_configuration” and setting alternate interface through “set_interface” to

the device will be ignored.

6.4.8.3.2 Data Stage

This stage is optional and defined only for requests that require data transfer. The direction of the

transfer is either from the host to the device (OUT packets) or from the device to the host (IN

packets). When an OUT packet is received from the host, the OUT interrupt will be generated, the

data stored in the USBDRn registers and the length recorded in the LEN bit field. Consequently the

TYPE bit field will be set to 0011

B

or ‘OUT packet’. Software is again required to read the registers

and set TYPE to ‘Empty’ at the end of this stage. The OUT interrupt is cleared by the reading of

USBDCR register.

The device can send an IN packet to the host. In this case software has to write the data packet in

the USBDRn registers, set the LEN bit field to the data length and set TYPE to 0101

B

or ‘IN packet’.

This will trigger the transmission of the packet over USB.

6.4.8.3.3 Status Stage

This stage is always performed to report the result of the requested operation. The direction is either

from the host to the device (OUT packets) or from the device to the host (IN packets). The data

length for this stage is always zero and the direction is always opposite to the direction of the

previous data stage (if any), or setup stage (if no data stage).

Содержание C541U

Страница 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Страница 7: ......

Страница 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Страница 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Страница 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Страница 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Страница 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...

Страница 192: ...Semiconductor Group 12 7 Index C541U ...