Semiconductor Group

7-1

1997-10-01

Interrupt System

C541U

7

Interrupt System

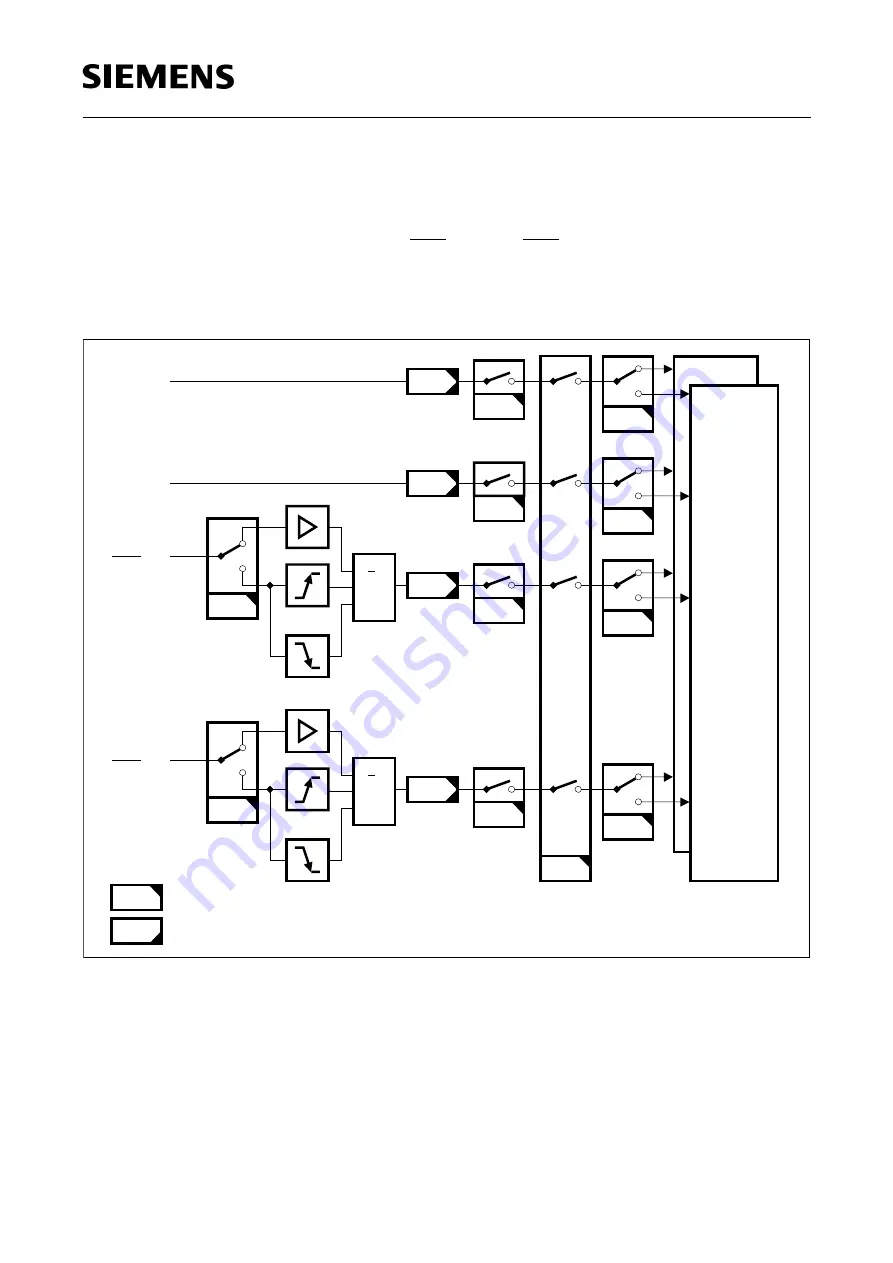

The C541U provides seven interrupt sources with two priority levels. Five interrupts can be

generated by the on-chip peripherals (timer 0, timer 1, SSC interface, and USB module), and two

interrupts may be triggered externally (P3.2/INT0 and P3.3/INT1).

Figure 7-1 and 7-2 give a general overview of the interrupt sources and illustrate the request and

control flags which are described in the next sections.

Figure 7-1

Interrupt Request Sources (Part 1)

EA

ET0

TF0

IEN0.1

TCON.5

000B

H

IEN0.7

Low Priority

MCT03684

Bit addressable

Request flag is cleared by hardware

IP0.1

PT0

High Priority

TCON.7

TF1

ET1

IEN0.3

H

001B

Timer 1

Timer 0

IEN0.0

TCON.1

IE0

0003

EX0

H

Overflow

Overflow

INT0

P3.2 /

IT0

TCON.0

ITCON.0

ITCON.1

>1

ITCON.3

TCON.2

P3.3 /

INT1

IT1

ITCON.2

>1

IEN0.2

TCON.3

IE0

0013

EX1

H

IP0.3

PT1

IP0.0

PX0

PX1

IP0.2

Содержание C541U

Страница 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Страница 7: ......

Страница 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Страница 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Страница 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Страница 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Страница 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...

Страница 192: ...Semiconductor Group 12 7 Index C541U ...