Semiconductor Group

7-7

1997-10-01

Interrupt System

C541U

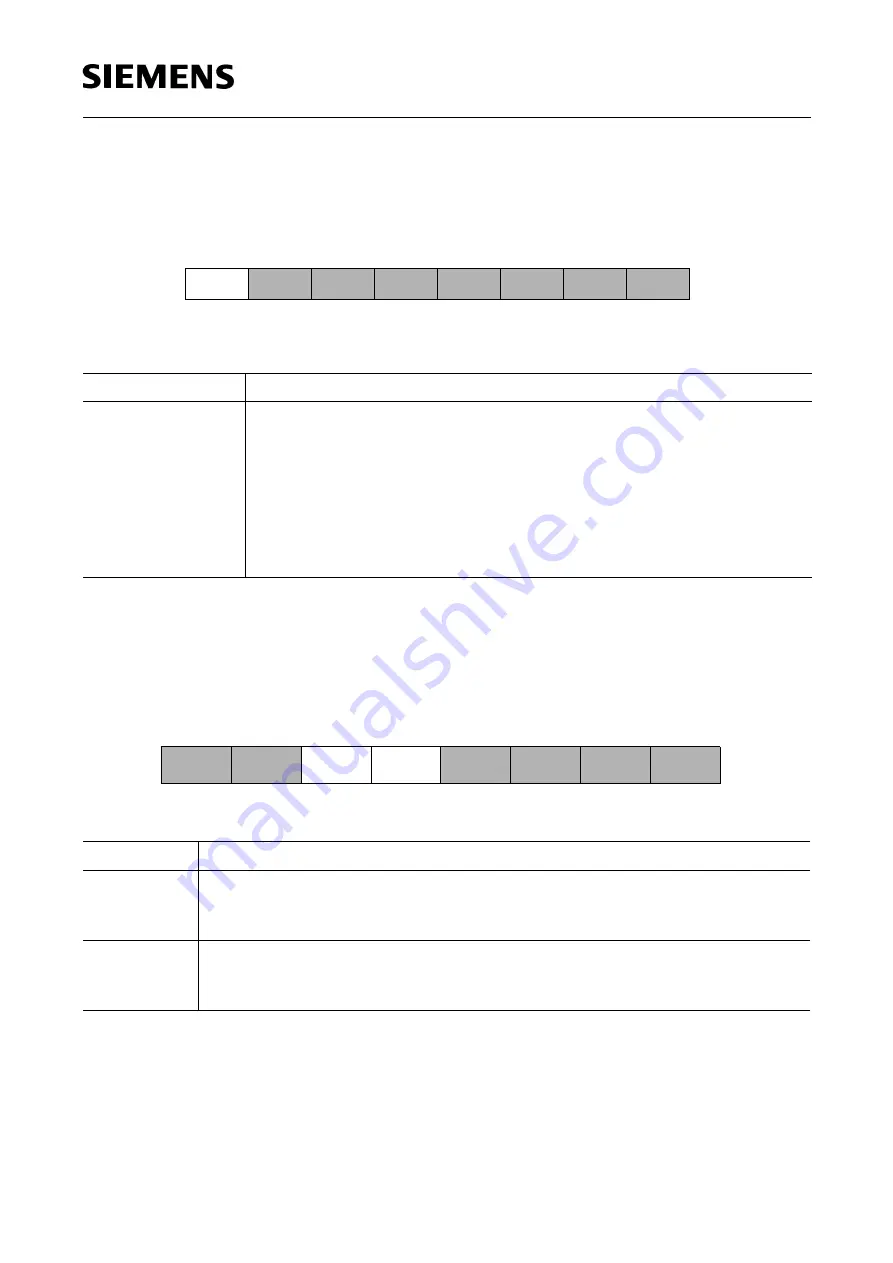

Special Function Register DPWDR (Address C2H)

Reset Value : 00H

Special Function Register USBPWD ( Address E6H) Reset Value : 00H

Bit

Function

DRVIE

Device request value interrupt enable

Setting bit DRVIE enables the generation of a device interrupt each time the

host sends device request that contains one or more of the following :

- Configuration Value (through SET_CONFIGURATION device request)

- Alternate Setting (through SET_INTERFACE device request)

- Interface (through SET_INTERFACE device request)

If DRVIE=0, the device request value interrupt is disabled.

If DRVIE=1, the device request value interrupt is enabled.

Bit

Function

SUSPIE

Suspend Interrupt Enable/Disable bit

0:

Suspend interrupt generation is disabled.

1:

Suspend interrupt generation is enabled.

DADDIE

Device Attach/Detach Interrupt Enable/Disable bit

0:

Interrupt generation upon DADD/P3.1 pin status is disabled.

1:

Interrupt generation upon DADD/P3.1 pin status is enabled.

DRVIE

0

0

0

0

0

TPWD RPWD

E6H

DPWDR

7

6

5

4

3

2

1

0

Bit No.

MSB

LSB

rw

r

r

r

r

r

rw

rw

MSB

LSB

USBPWD

7

6

5

4

3

2

1

0

Bit No.

E6H

r

rw

RPWD

TPWD

rw

DADD

SUSP

DADDIE

SUSPIE

0

0

r

rw

rw

r

r

Содержание C541U

Страница 1: ... 8 LW 026 0LFURFRQWUROOHU 8VHU V 0DQXDO http www siem ens d Sem iconductor ...

Страница 7: ......

Страница 21: ...Semiconductor Group 2 6 1997 10 01 Fundamental Structure C541U ...

Страница 37: ...Semiconductor Group 4 6 1997 10 01 External Bus Interface C541U ...

Страница 133: ...Semiconductor Group 6 88 1999 04 01 On Chip Peripheral Components C541U ...

Страница 163: ...Semiconductor Group 8 8 1997 10 01 Fail Safe Mechanisms C541U ...

Страница 185: ...Semiconductor Group 10 14 1997 10 01 OTP Memory Operation C541U ...

Страница 192: ...Semiconductor Group 12 7 Index C541U ...