Direct Memory Access Controller (DMAC)

User Manual All information provided in this document is subject to legal disclaimers. © REALTEK 2019. All rights reserved.

147

This field does not exist if the configuration parameter

DMAH_CH

x

_STAT_DST is set to False; in this case, the read-back value is

always 0.

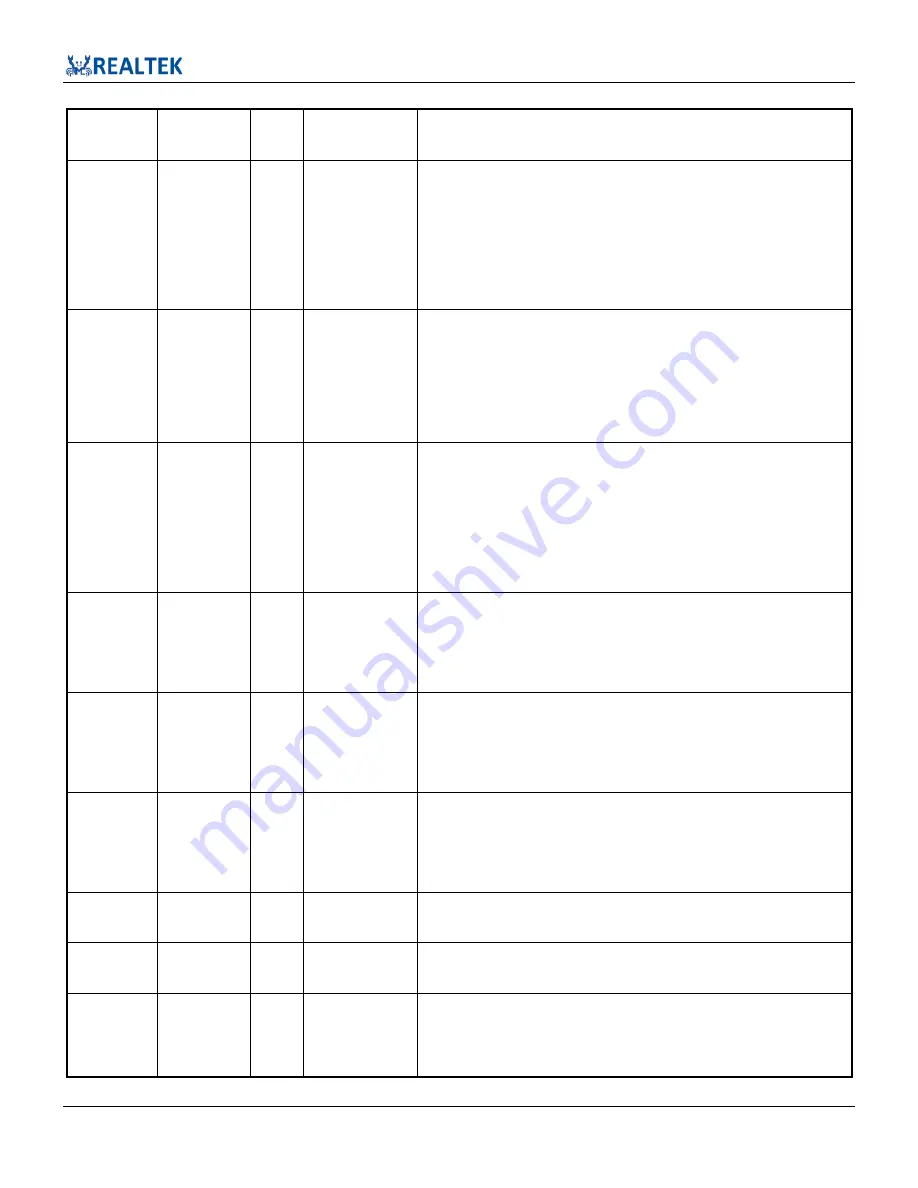

36:34

PROTCTL

R/W

0x1

Protection Control bits used to drive the AHB HPROT[3:1] bus.

The

AMBA Specification

recommends that the default value of HPROT

indicates a non-cached, non-buffered, privileged data access. The reset

value is used to indicate such an access.

HPROT[0] is tied high because all transfers are data accesses, as there are

no opcode fetches.

There is a one-to-one mapping of these register bits to the HPROT[3:1]

master interface signals. Table 9-18 shows the mapping of bits in this field

to the AHB HPROT[3:1] bus.

33

FIFO_MODE

R/W

0x0

FIFO Mode Select. Determines how much space or data needs to be

available in the FIFO before a burst transaction request is serviced.

0 = Space/data available for single AHB transfer of the specified transfer

width.

1 = Data available is greater than or equal to half the FIFO depth for

destination transfers and space available is greater than half the fifo depth

for source transfers. The exceptions are at the end of a burst transaction

request or at the end of a block transfer.

32

FCMODE

R/W

0x0

Flow Control Mode. Determines when source transaction requests are

serviced when the Destination Peripheral is the flow controller.

0 = Source transaction requests are serviced when they occur. Data pre-

fetching is enabled.

1 = Source transaction requests are not serviced until a destination

transaction request occurs. In this mode, the amount of data transferred

from the source is limited so that it is guaranteed to be transferred to the

destination prior to block termination by the destination. Data pre-fetching

is disabled.

31

RELOAD_DST

N/A

0x0

Automatic Destination Reload. The DARx register can be automatically

reloaded from its initial value at the end of every block for multi-block

transfers. A new block transfer is then initiated.

This register does not exist if the configuration parameter

DMAH_CH

x

_MULTI_BLK_EN is not selected; in this case, the read-back

value is always 0.

30

RELOAD_SRC

R/W

0x0

Automatic Source Reload. The SARx register can be automatically reloaded

from its initial value at the end of every block for multi-block transfers. A

new block transfer is then initiated.

This field does not exist if the configuration parameter

DMAH_CH

x

_MULTI_BLK_EN is not selected; in this case, the read-back

value is always 0.

29:20

MAX_ABRST

R/W

0x0

Maximum AMBA Burst Length. Maximum AMBA burst length that is used

for DMA transfers on this channel. A value of 0 indicates that software is

not limiting the maximum AMBA burst length for DMA transfers on this

channel. This field does not exist if the configuration parameter

DMAH_MABRST is not selected; in this case, the read-back value is always

0, and the maximum AMBA burst length cannot be limited by software.

19

SRC_HS_POL

R/W

0x0

Source Handshaking Interface Polarity.

0 = Active high

1 = Active low

18

DST_HS_POL

R/W

0x0

Destination Handshaking Interface Polarity.

0 = Active high

1 = Active low

17

LOCK_B

R/W

0x0

Bus Lock Bit. When active, the AHB bus master signal hlock is asserted for

the duration specified in CFG

x

.LOCK_B_L.

This field does not exist if the configuration parameter

DMAH_CH

x

_LOCK_EN is set to False; in this case, the read-back value is

always 0.

Realtek confidential files

The document authorized to

SZ99iot

2019-05-15 10:08:03