DE4 User Manual

29

www.terasic.com

June 20, 2018

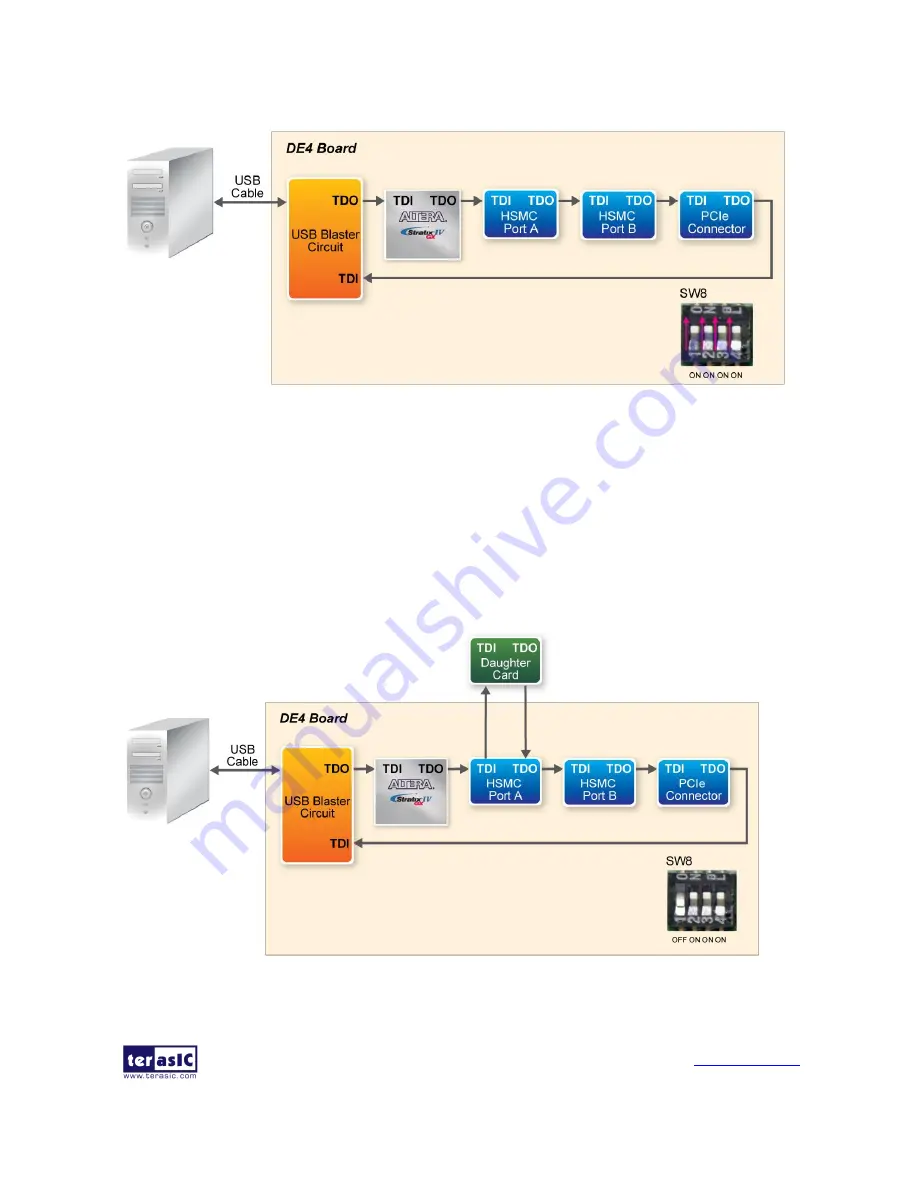

Figure 2

–14 JTAG chain for a standalone DE4 board

If the HSMC-based daughter card connected to the HSMC connector uses the JTAG interface, the

3-position DIP switch (SW8) is set to ‘Off’ to which HSMC port is used. In this case, from

Figure

2–15

HSMC port A is used where position 1 of the SW8 is set to ‘Off’. Similarly, if the JTAG

interface isn’t used on the HSMC-based daughter card, position 1 of SW8 is set to ‘On’ bypassing

the JTAG signals as shown in

Figure 2–16

.

Figure 2

–15 JTAG chain for a daughter card (uses JTAG) connected to HSMC port A of the DE4

Summary of Contents for ALTERA DE4

Page 1: ...DE4 User Manual 1 www terasic com June 20 2018 ...

Page 54: ...DE4 User Manual 54 www terasic com June 20 2018 ...

Page 83: ...DE4 User Manual 83 www terasic com June 20 2018 Figure 3 8 Access DDR2 SO DIMM memory ...

Page 92: ...DE4 User Manual 92 www terasic com June 20 2018 Figure 3 17 Fan Control of the DE4 ...

Page 150: ...DE4 User Manual 150 www terasic com June 20 2018 Figure 5 35 SOPC builder ...