ADuCM310 Hardware Reference Manual

UG-549

Rev. C | Page 43 of 192

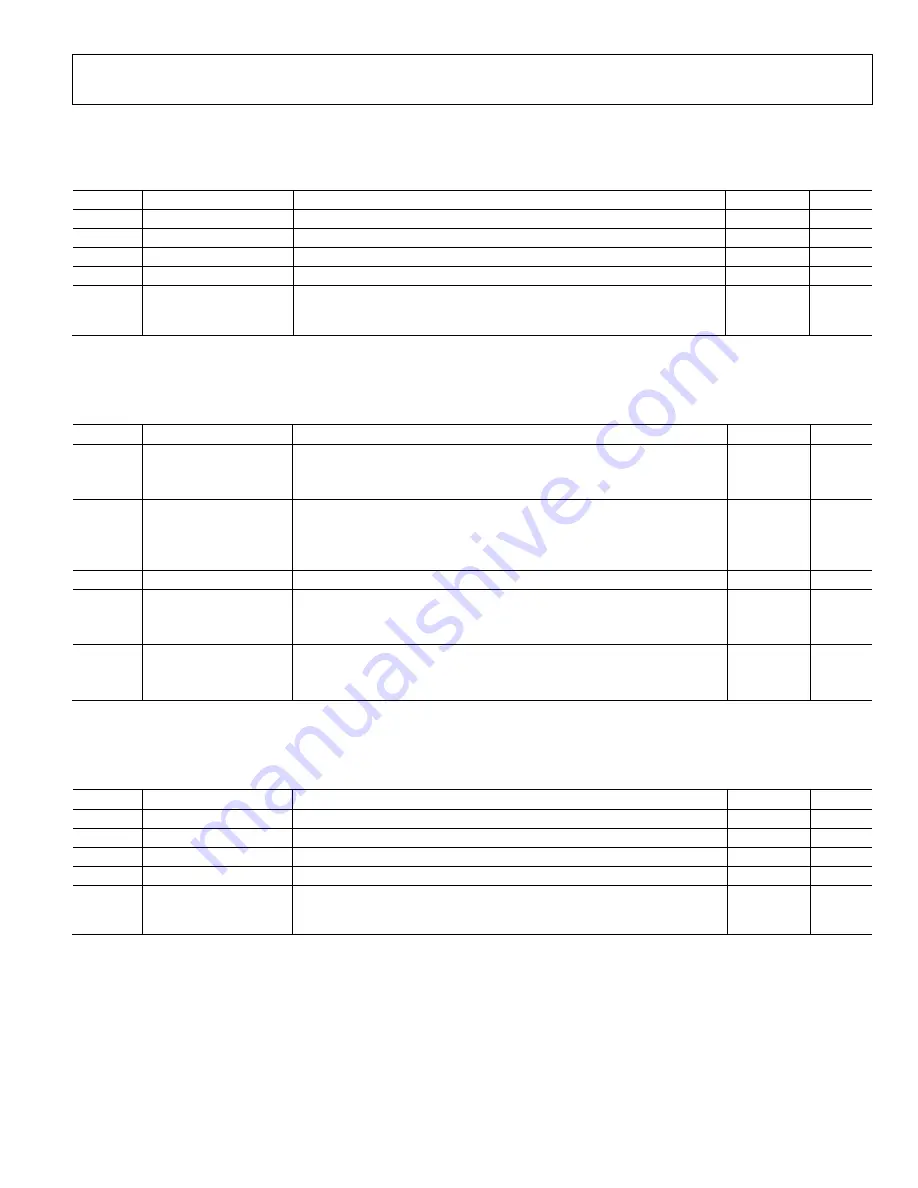

IDAC4 Data Register

Address: 0x40086820, Reset: 0x0000000000, Name: IDAC4DAT

Table 36. Bit Descriptions for IDAC4DAT

Bits

Bit Name

Description

Reset

Access

[31:28]

RESERVED

Reserved. Write 0.

0x0

R

[27:17]

DATH

IDAC4 high data.

0x0

RW

[16:12]

DATL

IDAC4 low data.

0x0

RW

[11:6]

RESERVED

Reserved.

0x0

R

[5:0]

SYNC

IDAC4 sync bits. These six bits are common to the six IDACs. Each bit set to

1 prevents the corresponding channel from updating immediately. The

channel updates when the bit changes to 0.

0x00

RW

IDAC4 Control Register

Address: 0x40086824, Reset: 0x01, Name: IDAC4CON

Table 37. Bit Descriptions for IDAC4CON

Bits

Bit Name

Description

Reset

Access

7

CLR

IDAC4 clear bit.

0x0

RW

0: clear IDAC1DAT.

1: enable write.

6

SHT_EN

IDAC4 shutdown enable. Enables automatic shutdown in case of

overtemperature.

0x0

RW

0: disable this function.

1: enable this function.

[5:2]

BW

IDAC4 bandwidth. See the IDAC Output Filter section for more details.

0x0

RW

1

PUL

IDAC4 pull down.

0x0

RW

0: disable the pull-down current source.

1: enable the pull-down current source.

0

PD

IDAC4 power down.

0x1

RW

0: powers up IDAC4.

1: powers down IDAC4.

IDAC5 Data Register

Address: 0x40086828, Reset: 0x00000000, Name: IDAC5DAT

Table 38. Bit Descriptions for IDAC5DAT

Bits

Bit Name

Description

Reset

Access

[31:28]

RESERVED

Reserved. Write 0.

0x0

R

[27:17]

DATH

IDAC5 high data.

0x0

RW

[16:12]

DATL

IDAC5 low data.

0x0

RW

[11:6]

RESERVED

Reserved.

0x0

R

[5:0]

SYNC

IDAC5 synchronization bits. These six bits are common to the six IDACs.

Each bit set to 1 prevents the corresponding channel from updating

immediately. The channel updates when the bit changes to 0.

0x00

RW