MOTOROLA CMOS LOGIC DATA

MC14536B

6–362

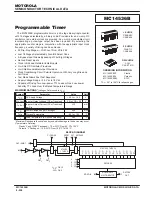

NOTE: When power is first applied to the device, Decode Out can be either at a high or low state.

On the rising edge of a Set pulse the output goes high if initially at a low state. The output

remains high if initially at a high state. Because Clock Inh is held high, the clock source on

the input pin has no effect on the output. Once Clock Inh is taken low, the output goes low

on the first negative clock transition. The output returns high depending on the 8–Bypass,

A, B, C, and D inputs, and the clock input period. A 2n frequency division (where n = the

number of stages selected from the truth table) is obtainable at Decode Out. A 20–divided

output of IN1 can be obtained at OUT1 and OUT2.

Figure 9. Time Interval Configuration Using an External Clock, Set,

and Clock Inhibit Functions

(Divide–by–2 Configured)

PULSE

GEN.

PULSE

GEN.

CLOCK

8–BYPASS

A

B

C

D

RESET

OSC INH

MONO–IN

SET

CLOCK INH

IN1

VSS

DECODE OUT

OUT 2

OUT 1

8

16

+V

6

9

10

11

12

2

14

15

1

7

3

13

5

4

DECODE OUT

CLOCK INH

SET

IN1

POWER UP

VDD

Содержание CMOS Logic

Страница 1: ......

Страница 5: ...iv MOTOROLA CMOS LOGIC DATA ...

Страница 6: ...Master Index 1 ...

Страница 12: ...Product Selection Guide 2 ...

Страница 17: ...The Better Program 3 ...

Страница 20: ...B and UB Series Family Data 4 ...

Страница 25: ...CMOS Handling and Design Guidelines 5 ...

Страница 32: ...CMOS Handling and Design Guidelines 5 ...

Страница 39: ...Data Sheets 6 ...

Страница 69: ...MOTOROLA CMOS LOGIC DATA 6 31 MC14008B Figure 5 Logic Diagram Cin A1 B1 A2 B2 A3 B3 A4 B4 S1 S2 S3 S4 Cout ...

Страница 234: ...MOTOROLA CMOS LOGIC DATA MC14174B 6 196 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Страница 238: ...MOTOROLA CMOS LOGIC DATA MC14175B 6 200 FUNCTIONAL BLOCK DIAGRAM TIMING DIAGRAM ...

Страница 555: ...CMOS Reliability 7 ...

Страница 561: ...Equivalent Gate Count 8 ...

Страница 563: ...Packaging Information Including Surface Mounts 9 ...

Страница 571: ......