312

9.5.2

A/D Converter Activation

The A/D converter can only be activated by channel 0 compare match A.

If the ADTE bit setting is 1 when the CMFA flag in 8TCSR0 is set to 1 by generation of channel 0

compare match A, an A/D conversion start request will be issued to the A/D converter. If the

TRGE bit in ADCR is 1 at this time, the A/D converter will be started. If the ADTE bit in

8TCSR0 is 1, A/D converter external trigger pin (

ADTRG

) input is disabled.

9.6

8-Bit Timer Application Example

Figure 9.17 shows how the 8-bit timer module can be used to output pulses with any desired duty

cycle. The settings for this example are as follows:

•

Clear the CCLR1 bit to 0 and set the CCLR0 bit to 1 in 8TCR so that 8TCNT is cleared by a

TCORA compare match.

•

Set bits OIS3, OIS2, OS1, and OS0 to (0110) in 8TCSR so that 1 is output on a TCORA

compare match and 0 is output on a TCORB compare match.

The above settings enable a waveform with the cycle determined by TCORA and the pulse width

detected by TCORB to be output without software intervention.

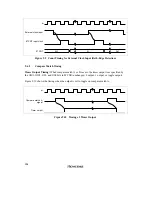

8TCNT

H'FF

Counter clear

TCORA

TCORB

H'00

TMO

Figure 9.17 Example of Pulse Output

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...