259

•

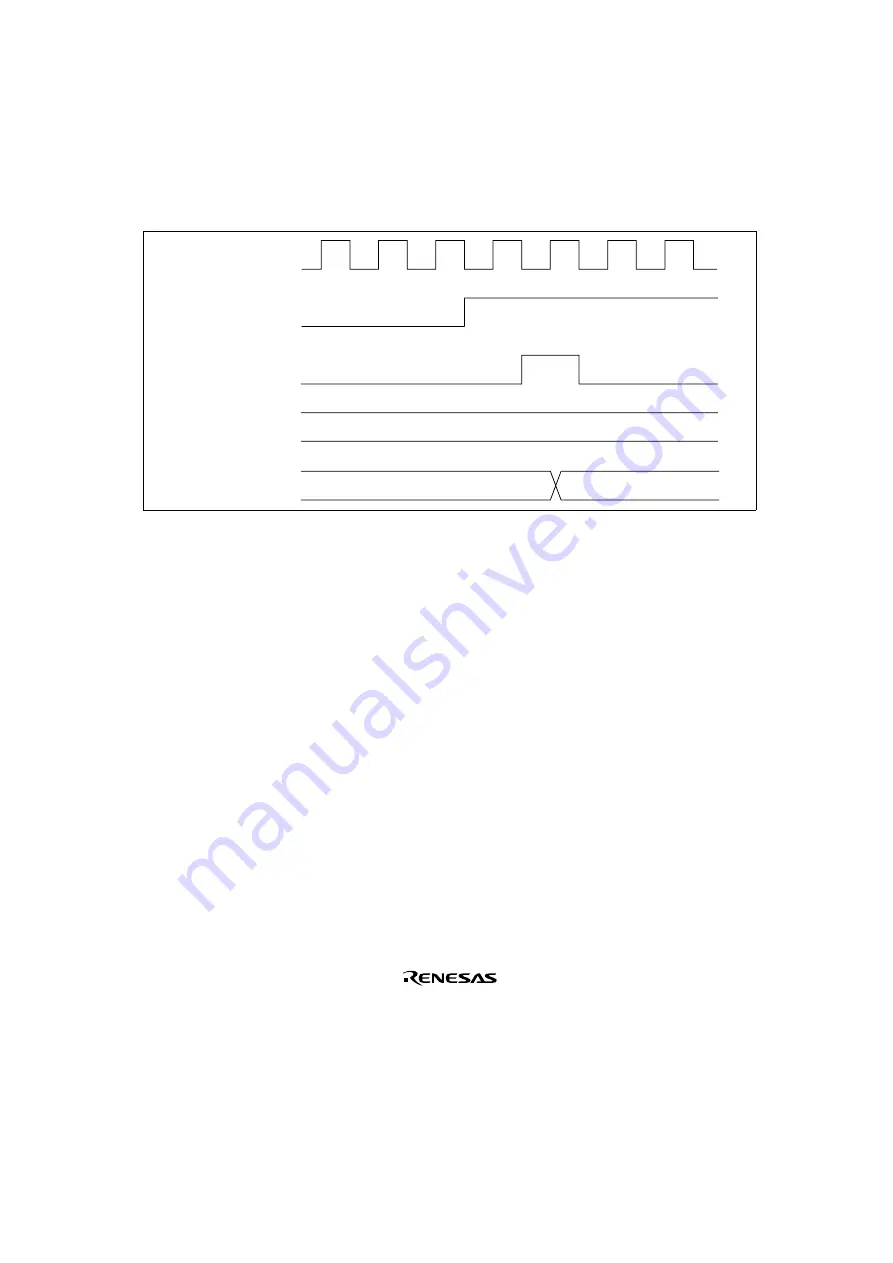

Input capture signal timing

Input capture on the rising edge, falling edge, or both edges can be selected by settings in

TIOR. Figure 8.23 shows the timing when the rising edge is selected. The pulse width of the

input capture signal must be at least 1.5 system clocks for single-edge capture, and 2.5 system

clocks for capture of both edges.

N

N

φ

Input-capture input

Input capture signal

16TCNT

GRA, GRB

Figure 8.23 Input Capture Signal Timing

8.4.3

Synchronization

The synchronization function enables two or more timer counters to be synchronized by writing

the same data to them simultaneously (synchronous preset). With appropriate 16TCR settings, two

or more timer counters can also be cleared simultaneously (synchronous clear). Synchronization

enables additional general registers to be associated with a single time base. Synchronization can

be selected for all channels (0 to 2).

Sample Setup Procedure for Synchronization: Figure 8.24 shows a sample procedure for

setting up synchronization.

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...