109

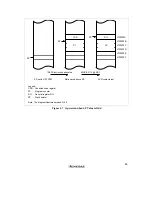

Figure 5.3 shows the timing of the setting of the interrupt flags (IRQnF).

φ

IRQn

IRQnF

input pin

Note: n = 5 to 0

Figure 5.3 Timing of Setting of IRQnF

Interrupts IRQ

0

to IRQ

5

have vector numbers 12 to 17. These interrupts are detected regardless of

whether the corresponding pin is set for input or output. When using a pin for external interrupt

input, clear its DDR bit to 0 and do not use the pin for chip select output, SCI input/output, or A/D

external trigger input.

5.3.2

Internal Interrupts

27 internal interrupts are requested from the on-chip supporting modules.

•

Each on-chip supporting module has status flags for indicating interrupt status, and enable bits

for enabling or disabling interrupts.

•

Interrupt priority levels can be assigned in IPRA and IPRB.

5.3.3

Interrupt Exception Handling Vector Table

Table 5.3 lists the interrupt exception handling sources, their vector addresses, and their default

priority order. In the default priority order, smaller vector numbers have higher priority. The

priority of interrupts other than NMI can be changed in IPRA and IPRB. The priority order after a

reset is the default order shown in table 5.3.

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...