883

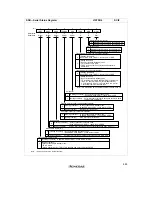

SSR—Serial Status Register

H’FFFB4

SCI0

Bit

Initial value

Read/Write

1

R/(W)

*

7

TDRE

0

R/(W)

*

6

RDRF

0

R/(W)

*

5

ORER

0

R/(W)

*

4

FER/ERS

0

R/(W)

*

3

PER

1

R

2

TEND

0

R

1

MPB

0

R/W

0

MPBT

Transmit end (for serial communication interface)

0

Multiprocessor bit transfer

0

1

Multiprocessor bit value in transmit data is 0

Multiprocessor bit value in transmit data is 1

Multiprocessor bit

0

1

Multiprocessor bit value in receive data is 0

Multiprocessor bit value in receive data is 1

[Clearing conditions]

Read TDRE when TDRE = 1, then write 0 in TDRE.

[Setting conditions]

• Reset or transition to standby mode

• TE is cleared to 0 in SCR.

• TDRE is 1 when last bit of 1-byte serial character is

transmitted.

Parity error

0

1

[Clearing conditions] • Reset or transition to standby mode

• Read PER when PER = 1, then write 0 in PER.

[Setting condition]

Parity error (parity of receive data does not match parity

setting of O/

E

bit in SMR)

Framing error (for serial communication interface)

0

[Clearing conditions]

• Reset or transition to standby mode

• Read FER when FER = 1, then write 0 in FER.

[Setting condition]

Framing error (stop bit is 0)

Error signal status (for smart card interface)

0

[Clearing conditions]

• Reset or transition to standby mode

• Read ERS when ERS = 1, then write 0 in ERS.

[Setting condition]

A low error signal is received.

1

1

Overrun error

0

[Clearing conditions]

• Reset or transition to standby mode

• Read ORER when ORER = 1, then write 0 in ORER.

[Setting condition]

Overrun error (reception of the next serial data ends when RDRF = 1)

1

Receive data register full

0

[Clearing conditions]

• Reset or transition to standby mode

• Read RDRF when RDRF = 1, then write 0 in RDRF.

[Setting condition]

Serial data is received normally and transferred from RSR to RDR.

1

Transmit data register empty

Note:

*

Only 0 can be written, to clear the flag.

0

[Clearing conditions] • Read TDRE when TDRE = 1, then write 0 in TDRE.

[Setting conditions]

• Reset or transition to standby mode

• TE is 0 in SCR.

• Data is transferred from TDR to TSR, enabling new data to be written in TDR

1

1

Transmit end (for smart card interface)

0

[Clearing conditions]

Read TDRE when TDRE = 1, then write 0 in TDRE.

[Setting conditions]

• Reset or transition to standby mode

• TE is cleared to 0 in SCR and FER/ERS is cleared to 0.

• TDRE is 1 and FER/ERS is 0 (normal transmission)

2.5 etu* (when GM = 0) or 1.0 etu (when GM = 1) after

1-byte serial character is transmitted.

1

Note:

*

etu: Elementary time unit (time required to transmit one bit)

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...