451

data register are reserved bits that are always read as 0. Table 14.3 indicates the pairings of analog

input channels and A/D data registers.

The CPU can always read and write the A/D data registers. The upper byte can be read directly,

but the lower byte is read through a temporary register (TEMP). For details see section 14.3, CPU

Interface.

The A/D data registers are initialized to H'0000 by a reset and in standby mode.

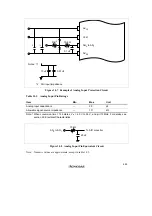

Table 14.3

Analog Input Channels and A/D Data Registers (ADDRA to ADDRD)

Analog Input Channel

Group 0

Group 1

A/D Data Register

AN

0

AN

4

ADDRA

AN

1

AN

5

ADDRB

AN

2

AN

6

ADDRC

AN

3

AN

7

ADDRD

14.2.2

A/D Control/Status Register (ADCSR)

Bit

Initial value

Read/Write

7

ADF

0

R/(W)

*

6

ADIE

0

R/W

5

ADST

0

R/W

4

SCAN

0

R/W

3

CKS

0

R/W

0

CH0

0

R/W

2

CH2

0

R/W

1

CH1

0

R/W

Note:

*

Only 0 can be written, to clear the flag.

A/D end flag

Indicates end of A/D conversion

A/D interrupt enable

Enables and disables A/D end interrupts

A/D start

Starts or stops A/D conversion

Scan mode

Selects single mode or scan mode

Clock select

Selects the A/D conversion time

Channel select 2 to 0

These bits select analog

input channels

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...