461

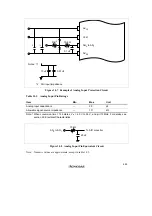

Table 14.4

A/D Conversion Time (Single Mode)

CKS = 0

CKS = 1

Symbol

Min

Typ

Max

Min

Typ

Max

Synchronization delay

t

D

6

—

9

4

—

5

Input sampling time

t

SPL

—

31

—

—

15

—

A/D conversion time

t

CONV

131

—

134

69

—

70

Note:

Values in the table are numbers of states.

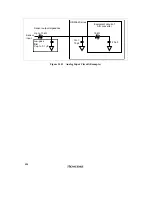

14.4.4

External Trigger Input Timing

A/D conversion can be externally triggered When the TRGE bit is set to 1 in ADCR and the 8-bit

timer's ADTE bit is cleared to 0, external trigger input is enabled at the

ADTRG

pin. A high-to-

low transition at the

ADTRG

pin sets the ADST bit to 1 in ADCSR, starting A/D conversion.

Other operations, in both single and scan modes, are the same as if the ADST bit had been set to 1

by software. Figure 14.6 shows the timing.

φ

ADTRG

Internal trigger

signal

ADST

A/D conversion

Figure 14.6 External Trigger Input Timing

Содержание H8/3060

Страница 10: ......

Страница 16: ......

Страница 114: ...66 ...

Страница 132: ...84 ...

Страница 144: ...96 ...

Страница 170: ...122 ...

Страница 212: ...164 ...

Страница 268: ...220 ...

Страница 332: ...284 ...

Страница 396: ...348 ...

Страница 494: ...446 ...

Страница 698: ...650 ...

Страница 729: ...681 H8 3062F ZTAT or H8 3062F ZTAT R mask version Ports 1 2 5 LED 600 Ω Figure 22 5 Sample LED Circuit ...

Страница 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Страница 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Страница 810: ...762 ...

Страница 994: ...946 ...