MC97F6108A User’s manual

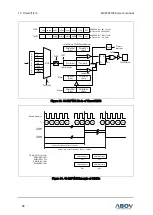

10. Timer0/1/2/3

91

TxCR1 (Timer0/1/23 Mode Control Register 1) : B3H, BBH, C3H, CBH

7

6

5

4

3

2

1

0

-

-

TxIN[2]

TxIN[1]

TxIN[0]

ECEN

Tx_PE

POL

-

-

R/W

R/W

R/W

R/W

R/W

R/W

Initial value: 00

H

TxIN[2:0]

Select Event Counter and External Interrupt for Capture mode

TxIN2

TxIN1

TxIN0

description

0

0

0

TxEC0

0

0

1

TxEC1

0

1

0

TxCAP0

0

1

1

TxCAP1

1

0

0

TxCAP2

1

0

1

-

1

1

0

-

1

1

1

-

ECEN

Control Event Counter

0

Event Counter disable

1

Event Counter enable

Tx_PE

Control Timer X Output port

0

Timer X Output disable

1

Timer X Output enable

POL

Configure PWM polarity

0

Negative (Duty Match: Clear)

1

Positive (Duty Match: Set)

TxL (Timer0/1/2/3 Register Low, Read Case) : B4H, BCH, C4H, CCH

7

6

5

4

3

2

1

0

TxL7

TxL6

TxL5

TxL4

TxL3

TxL2

TxL1

TxL0

R

R

R

R

R

R

R

R

Initial value: 00

H

TxL[7:0]

TxL Counter Period Low data.

CDRxL (Capture0/1/2/3 Data Register Low, Read Case) : B4H, BCH, C4H, CCH

7

6

5

4

3

2

1

0

CDRxL07

CDRxL06

CDRxL05

CDRxL04

CDRxL03

CDRxL02

CDRxL01

CDRxL00

R

R

R

R

R

R

R

R

Initial value: 00

H

CDRxL[7:0]

Tx Capture Low data.