15. USART

MC97F6108A User’s manual

154

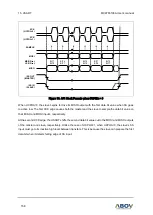

Even if there’s 2nd stop bit in the frame, th

e 2nd stop bit is ignored by Receiver. That is, receiving the

first stop bit means that a complete serial frame is present in the receiver shift register and contents of

the shift register are to be moved into the receive buffer. The receive buffer is read by reading the

UDATA register.

If 9-bit characters are used (USIZE[2:0] = 7), the ninth bit is stored in RX8 bit field in the UCTRL3

register. The 9th bit must be read from the RX8 bit before reading the low 8 bits from the UDATA register.

Likewise, error flags FE, DOR, PE must be read before reading data from UDATA register. This is

because the error flags are stored in the same FIFO position of the receive buffer.

15.8.2

Receiver flag and interrupt

USART Receiver has one flag that indicates the Receiver state. Receive Complete (RXC) flag indicates

whether there are unread data present in the receive buffer. This flag is set when there are unread data

in the receive buffer and cleared when the receive buffer is empty. If the Receiver is disabled (RXE=0),

the receiver buffer is flushed and the RXC flag is cleared.

When Receive Complete Interrupt Enable (RXCIE) bit in the UCTRL2 register is set and Global Interrupt

is enabled, USART Receiver Complete Interrupt is generated while RXC flag is set.

USART Receiver has three error flags such as Frame Error (FE), Data OverRun (DOR) and Parity Error

(PE). These error flags can be read from USTAT register. As data received are stored in the 2-level

receive buffer, these error flags are also stored in the same position of receive buffer. So, before reading

received data from UDATA register, read the USTAT register first which contains error flags.

Frame Error (FE) flag indicates the state of the first stop bit. The FE flag is set when the stop bit was

correctly detected as “1”, and the FE flag is cleared when the stop bit was incorrect, i.e. detected as “0”.

This flag can be used for detecting out-of-sync conditions between data frames.

Data Over Run (DOR) flag indicates data loss due to a receive buffer’s full condition. The DOR occurs

when the receive buffer is full, and another new data is present in the receive shift register which are to

be stored into the receive buffer. After the DOR flag is set, all the incoming data are lost. To prevent

data loss or clear this flag, read the receive buffer.

Parity Error (PE) flag indicates that the frame in the receive buffer had a Parity Error when received. If

Parity Check function is not enab

led (UPM[1] = 0), the PE bit is always read “0”.

NOTE

: The error flags related to the receive operation are not used when USART is in SPI mode.

15.8.3

Parity checker

If Parity bit is enabled (UPM[1]=1), Parity Checker calculates parity of data bits of incoming frames and

compares the result with the parity bit of the received serial frame.