6. Interrupt controller

MC97F6108A User’s manual

50

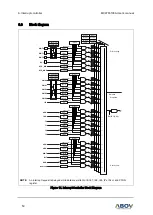

6.3

Block diagram

Release

Stop/Idle

EA(IE.7[A8

H

])

Priority High

Priority Low

FLAG0

FLAG1

FLAG2

FLAG3

IE[A8

H

]

EIFLAG.0 [A4

H

]

EIFLAG.1 [A4

H

]

EIFLAG.2 [A4

H

]

EIFLAG.3 [A4

H

]

EINT0

EINT1

PCI

0

1

2

3

4

5

0

1

2

3

4

5

0

1

2

3

4

5

0

1

2

3

4

5

EIEDGE[A5

H

]

IP[92

H

]

IPH[93

H

]

EIPOLA[A6

H

]

EIBOTH[A7

H

]

IE2[AA

H

]

12

13

14

15

16

17

12

13

14

15

16

17

12

13

14

15

16

17

12

13

14

15

16

17

ATP_MIN

ATPCR.6 [F9

H

]

ATP_MAX

ATPCR.7 [F9

H

]

IE1[A9

H

]

6

7

8

9

10

11

6

7

8

9

10

11

6

7

8

9

10

11

CMP0IF

CMP0

CIFLAG.0 [AC

H

]

CMP1IF

CMP2IF

CMP3IF

CMP4IF

CMP1

CMP2

CMP3

CMP4

CIFLAG.1 [AC

H

]

CIFLAG.2 [AC

H

]

CIFLAG.3 [AC

H

]

CIFLAG.4 [AC

H

]

IIF

I2C

I2CMR.7 [DA

H

]

RXC

USTAT.5 [FD

H

]

RXD

TXC

TXD

USTAT.6 [FD

H

]

TMIF0

T0

TMISR.0 [D5

H

]

TMIF1

T1

TMISR.1 [D5

H

]

TMIF2

T2

TMISR.2 [D5

H

]

TMIF3

T3

TMISR.3 [D5

H

]

IE3[AB

H

]

18

19

20

21

22

23

18

19

20

21

22

23

18

19

20

21

22

23

18

19

20

21

22

23

PPGIF

PPGCR2.7 [E1

H

]

PPG

AFLAG

ADC

ADCM.4 [95

H

]

WDTIFR

WDT

WDTMR.0 [8D

H

]

BITF

BIT

BCCR.7 [8B

H

]

BODRF

BOD

RSFR.3 [86

H

]

-

reserved

-

6

7

8

9

10

11

IP1[9A

H

]

IP1H[9B

H

]

IP2[9C

H

]

IP2H[9D

H

]

IP3[9E

H

]

IP3H[9F

H

]

ATP_MIN

ATP_MAX

CIEDGE[AD

H

]

CIPOLA[AE

H

]

CIBOTH[AF

H

]

EINT2

NOTE:

An interrupt request is delayed while data are written to IE, IE1, IE2, IE3, IPx, IPxH, and PCON

register.

Figure 14. Interrupt Controller Block Diagram