6. Interrupt controller

MC97F6108A User’s manual

46

6

Interrupt controller

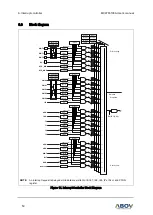

MC97F6108A supports up to 23 interrupt sources. The interrupts have separate enable register bits

associated with them, allowing software control. In addition, they have four levels of priority assigned

to themselves.

A non-maskable interrupt source is always enabled with a higher priority than any other interrupt

sources, and is not controllable by software.

Interrupt controller of MC97F6108A has following features:

Request receive from the 23 interrupt sources

6 groups of priority

4 levels of priority

Multi Interrupt possibility

A request of higher priority level is served first, when multiple requests of different priority

levels are received simultaneously.

Each interrupt source can be controlled by EA bit and each IEx bit

Interrupt latency of 5 to 8 machine cycles in single interrupt system

A non-maskable interrupt is always enabled, while maskable interrupts are enabled through four pairs

of interrupt enable registers (IE, IE1, IE2, and IE3). Each bit of IE, IE1, IE2, IE3 register individually

enables/disables the corresponding interrupt source. Overall control is provided by bit 7 of IE (EA).

When EA is set to ‘0’, all interrupts are disabled: when EA is set to ‘1’, interrupts are individually enabled

or disabled through the other bits of the interrupt enable reg

isters. The EA bit is always cleared to ‘0’

jumping to an interrupt service vector and set to ‘1’ executing the [RETI] instruction. The

MC97F6108A

supports a four-level priority scheme. Each maskable interrupt is individually assigned to one of four

priority levels according to IP, IPH, IP1, IP1H, IP2, IP2H, IP3 and IP3H.