MC97F6108A User’s manual

15. USART

153

UDRE flag indicates whether the transmit buffer is ready to be loaded with new data. This bit is set

when the transmit buffer is empty and cleared when the transmit buffer contains transmission data

which has not yet been moved into the shift register. And also this flag can be cleared by writing ‘0’ to

this bit field. Writing ‘1’ to this field is not valid.

When Data Register Empty Interrupt Enable (UDRIE) bit in UCTRL2 register is set and Global Interrupt

is enabled, USART2 Data Register Empty Interrupt is generated while UDRE flag is set.

Transmit Complete (TXC) flag bit is set when the entire frame in the transmit shift register has been

shifted out and there are no more data in the transmit buffer. The TXC flag is automatically cleared

when the Transmit Complete Interrupt service routine is executed, or it can be cleared by writing ‘0’ to

TXC bit in USTAT register.

When Transmit Complete Interrupt Enable (TXCIE) bit in UCTRL2 register is set and the Global

Interrupt is enabled, USART Transmit Complete Interrupt is generated while TXC flag is set.

15.7.3

Parity generator

Parity Generator calculates the parity bit for the sending serial frame data. When parity bit is enabled

(UPM[1] = 1), transmitter control logic inserts the parity bit between bits and the first stop bit of the

sending frame.

15.7.4

Disabling transmitter

Disabling the Transmitter by clearing TXE bit will not become effective until ongoing transmission is

completed. When the Transmitter is disabled, the TXD pin is used as normal General Purpose I/O

(GPIO) or primary function pin.

15.8

USART receiver

USART Receiver is enabled by setting the RXE bit in the UCTRL1 register. When Receiver is enabled,

normal pin operation of RXD pin is overridden by the USART as the serial input pin of Receiver. Baud

rate, mode of operation and frame format must be set before serial reception. If synchronous or SPI

operation is used, a clock on the XCK pin will be used as a transfer clock. If USART operates in SPI

mode, SS pin is used as SS input pin in slave mode or can be configured as SS output pin in master

mode. This can be done by setting SPISS bit in UCTRL3 register.

15.8.1

Receiving Rx data

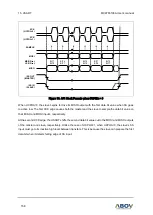

When USART is in synchronous or asynchronous operation mode, Receiver starts data reception when

it detects a valid start bit (LOW) on RXD pin. Each bit following the start bit is sampled at pre-defined

baud rate (asynchronous) or sampling edge of XCK (synchronous), and shifted into a receive shift

register until the first stop bit of a frame is received.