MC97F6108A User’s manual

7. Clock generator

75

7

Clock generator

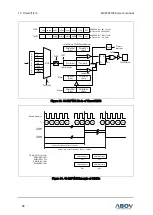

As shown in Figure 23, a clock generator produces basic clock pulses which provide a system clock for

CPU and peripheral hardware.

It contains main frequency clock oscillator. The internal RC oscillator is only used as system clock. The

default system clock is internal RC Oscillator and the default division rate is one.

Default system clock is 16MHz INT-RC Oscillator. To stabilize the system internally, internal 8kHz WDT

oscillator for BIT, WDT and ports de-bounce on POR is recommended.

Oscillators in the clock generator are introduced in the followings:

Calibrated high internal RC oscillator (16MHz)

—

INTRC OSC/1 (16MHz, default system clock)

—

INTRC OSC/2 (8MHz)

—

INTRC OSC/4 (4MHz)

—

INTRC OSC/8 (2MHz)

7.1

Clock generator block diagram

In this section, a clock generator of MC97F6108A is described in a block diagram.

SCLK = fX

(Core, System, Peripheral)

SYSCK[1:0]

WDTRCON

BIT

clock

Stabilization

Time

Generation

WDTCK

BITWDTRC

fWDTRC

System Clock

Generator

Clock

Change

DIV

fSYS

INTRC-OSC

(16MHz)

WDTRC-OSC

(8kHz)

M

U

X

M

U

X

1/2048

1/256

1/16

1/2

BITCK[1:0]

BIT

M

U

X

BIT

overflow

WDT

clock

WDT

WDT

overflow

1/1

1/2

1/4

1/8

fINTRC

Figure 23. Clock Generator Block Diagram