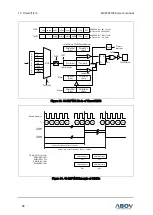

8. Basic Interval Timer (BIT)

MC97F6108A User’s manual

78

8.3

BIT register description

BITCR (Basic Interval Timer Control Register): 8BH

7

6

5

4

3

2

1

0

BITF

BCK2

BCK1

BWDTRC

BCLR

BPD2

BPD1

BPD0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value: 45H

BITF

When BIT Interrupt occurs, this bit becomes

‘1’. For clearing bit, write ‘0’ to

this bit or auto clear by INT_ACK signal

0

BIT interrupt no generation

1

BIT interrupt generation

BCK[1:0]

Select BIT clock source

BCK1

BCK0

Description

0

0

fBIT/2048 (default)

0

1

fBIT/256

1

0

fBIT/16

1

1

fBIT/2

BWDTRC

Select BIT Clock Source (fBIT) to WDTRC

0

fSYS

1

fWDTRC

BCLR

If this bit is written to

‘1’, BIT Counter is cleared to ‘0’

After one machine cycle BCLR is cleared automatically.

0

Free Running

1

Clear Counter

BPD[2:0]

Select BIT overflow period

BPD2

BPD1

BPD0

Description

(BIT Clock

≒

7.8kHz, default)

0

0

0

0.256ms (BIT Clock * 2)

0

0

1

0.512ms (BIT Clock * 4)

0

1

0

1.024ms (BIT Clock * 8)

0

1

1

2.048ms (BIT Clock * 16)

1

0

0

4.096ms (BIT Clock * 32)

1

0

1

8.192ms (BIT Clock * 64) (default)

1

1

0

16.384ms (BIT Clock * 128)

1

1

1

32.768ms (BIT Clock * 256)

BITR (Basic Interval Timer Register): 8CH

7

6

5

4

3

2

1

0

BIT7

BIT6

BIT5

BIT4

BIT3

BIT2

BIT1

BIT0

R

R

R

R

R

R

R

R

Initial value: 00H

BIT[7:0]

BIT Counter