22

6

F

2

S

0

8

5

0

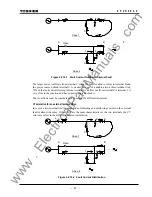

time difference between send and receive terminals is less than the PDTD setting and the SYNC

ALARM LED is off. If these conditions are not satisfied, the operation may cause a false

tripping.

Note: The mode change with the binary input signal is performed by either way:

•

If the binary input contact is such as to be open when the relay is in service, set

the BI to "Inv" (inverted). The mode changes when the contact is closed more

than 2 seconds and then open.

•

If the binary input contact is such as to be closed when the relay is in service, set

the BI to "Norm" (normal). The mode changes when the contact is open more

than 2 seconds and then closed.

For the BISW4, see Section 3.2.1.

In the three-terminal application, the mode change to Mode 2B is available even

when one of the three communication routes is failed.

Mode 2B

: The same intra-system synchronization as in Mode 2A is applied.

When the GPS signal has been restored, the mode shifts from Mode 2B to Mode 0.

If a failure occurs in the communication system, the sampling timing adjustment is disabled and

each terminal runs free.

The mode shifts from Mode 2B to Mode 2A, when the apparent load current phase difference

exceeds the value determined by the PDTD setting for pre-determined time.

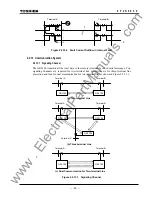

Checking the current phase difference (For two-terminal application setting only)

The current phase difference is checked using the following equations:

I

1A

⋅

cos

θ

< 0

I

1A

⋅

I

1B

sin

θ

< I

1A

⋅

I

1B

sin

θ

s

I

1A

> OCCHK

I

1B

> OCCHK

Where,

I

1A

= Positive sequence component of load current at local terminal

I

1B

= Positive sequence component of load current at remote terminal

θ

= Phase difference of I

1B

from

-

I

1A

θ

s = Critical phase difference

= CHK

θ

‐

HYS

θ

CHK

θ

=

PDTD(

µ

s)

2

×

360

°

20000(

µ

s)

+ 8.5

°

HYS

θ

= Margin of phase difference checking

OCCHK = Minimum current for phase difference check

If the magnitude of I

1A

and I

1B

exceed the setting and the conditions for both equations above are

established, then the sampling is regarded to be synchronized.

If the current phase difference exceeds a set value, the "SYNC ALARM" LED on the front panel

is lit.

Checking the current phase difference is enabled by setting the scheme switches [TERM] to

"2TERM" and [SRC

θ

] to "I".

www

. ElectricalPartManuals

. com

Summary of Contents for GRL100-701B

Page 329: ... 328 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 339: ... 338 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 351: ... 350 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 381: ... 380 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 413: ... 412 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 417: ... 416 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 453: ... 452 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 457: ... 456 6 F 2 S 0 8 5 0 w w w E l e c t r i c a l P a r t M a n u a l s c o m ...

Page 473: ...w w w E l e c t r i c a l P a r t M a n u a l s c o m ...