S

Device Addr

Rd

A

Byte #0

A

PEC

NA

P

S

Device Addr

Rd

A

Byte #0

NA

P

S

Device Addr

Wr

A

Byte #0

A

PEC

A

P

S

Device Addr

Wr

A

Byte #0

A

P

S

Device Addr

R/W

A

P

Master Mode Operation Reference

373

SNIU028A – February 2016 – Revised April 2016

Copyright © 2016, Texas Instruments Incorporated

PMBus Interface/I2C Interface

10.7.1 Quick Command

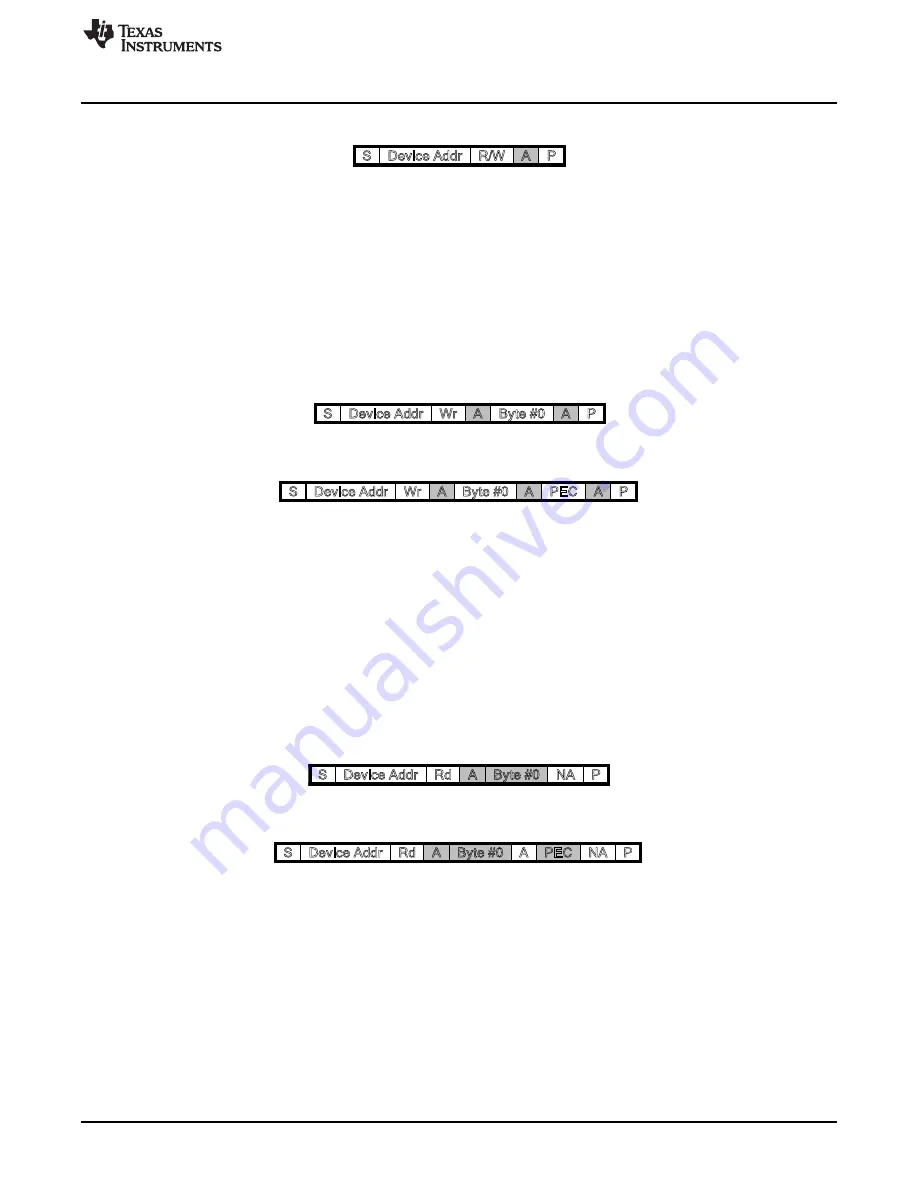

Figure 10-22. Quick Command Format

Quick commands are initiated in Master Mode by simply programming the desired slave device address

into the Master Control Register. The byte count within the Master Control Register is configured to 0

bytes by writing all zeros to bits 15-8. Upon transmission of the device address, the PMBus Interface will

monitor the slave acknowledgement of the address. If the address is not acknowledged, the Nacked bit

within the status register is enabled and the PMBus Interface automatically enables a stop condition on

the PMBus to terminate the message. If the address is acknowledged, a data request is issued to the

processor. The firmware writes a ‘0’ to the Acknowledge Register to terminate the message, forcing the

PMBus Interface to write a stop condition onto the PMBus.

10.7.2 Send Byte

Figure 10-23. Send Byte w/o PEC Byte

Figure 10-24. Send Byte with PEC Byte

A Send Byte message consists of the device address, a single data byte and an optional PEC byte. To

initiate a Send Byte message, the data byte to be transmitted to the slave is loaded into bits 7-0 of the

Transmit Data Register. The Master Control Register is configured with the device address. To transmit a

PEC byte with the message, the PEC_EN bit within the Master Control Register is asserted high when the

address is programmed.

After programming the Master Control Register, the PMBus Interface initiates the Send Byte message

onto the PMBus. The firmware can wait for an End of Message interrupt from the PMBus Interface. Upon

receipt of the EOM interrupt, the Status Register is read to verify the slave properly acknowledged the

transmitted data.

10.7.3 Receive Byte

Figure 10-25. Receive Byte w/o PEC Byte

Figure 10-26. Receive Byte with PEC Byte

A Receive Byte message consists of the device address, a single data byte and an optional PEC byte.

Data is being read from the slave in a Receive Byte message. To initiate a Receive Byte message, the

firmware programs the device address, the R/W bit and the optional PEC_EN into the Master Control

Register. The R/W bit is enabled high to indicate a read message type (data transmitted from Slave to

Master).