CHAPTER 17 SERIAL INTERFACE IIC0

Preliminary User’s Manual U17260EJ3V1UD

416

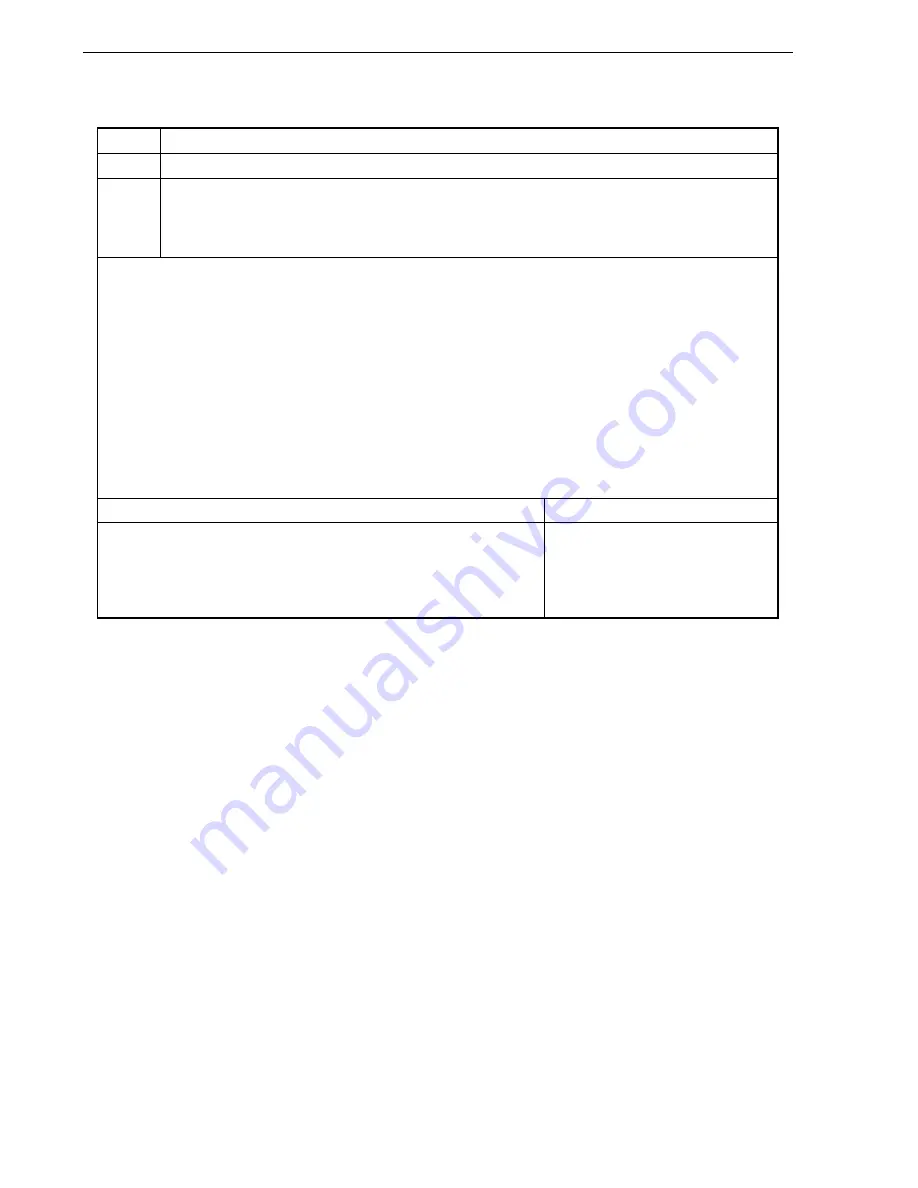

Figure 17-5. Format of IIC Control Register 0 (IICC0) (4/4)

SPT0

Stop condition trigger

0

Stop condition is not generated.

1

Stop condition is generated (termination of master device’s transfer).

After the SDA0 line goes to low level, either set the SCL0 line to high level or wait until it goes to high level. Next,

after the rated amount of time has elapsed, the SDA0 line changes from low level to high level and a stop

condition is generated.

Cautions concerning set timing

•

For master reception:

Cannot be set to 1 during transfer.

Can be set to 1 only in the waiting period when ACKE0 has been cleared to 0 and slave has been

notified of final reception.

•

For master transmission: A stop condition cannot be generated normally during the acknowledge period. Therefore, set it

during the wait period that follows output of the ninth clock.

•

Cannot be set to 1 at the same time as STT0.

•

SPT0 can be set to 1 only when in master mode

Note

.

•

When WTIM0 has been cleared to 0, if SPT0 is set to 1 during the wait period that follows output of eight clocks, note that a

stop condition will be generated during the high-level period of the ninth clock. WTIM0 should be changed from 0 to 1 during

the wait period following the output of eight clocks, and SPT0 should be set to 1 during the wait period that follows the output

of the ninth clock.

•

Setting SPT0 to 1 and then setting it again before it is cleared to 0 is prohibited.

Condition for clearing (SPT0 = 0)

Condition for setting (SPT0 = 1)

•

Cleared by loss in arbitration

•

Automatically cleared after stop condition is detected

•

Cleared by LREL0 = 1 (exit from communications)

•

When IICE0 = 0 (operation stop)

•

Reset

•

Set by instruction

Note

Set SPT0 to 1 only in master mode. However, SPT0 must be set to 1 and a stop condition generated before

the first stop condition is detected following the switch to the operation enabled status. For details, see

17.5.15 Other cautions

.

Caution When bit 3 (TRC0) of IIC status register 0 (IICS0) is set to 1, WREL0 is set to 1 during the ninth

clock and wait is canceled, after which TRC0 is cleared and the SDA0 line is set to high

impedance.

Remark

Bit 0 (SPT0) becomes 0 when it is read after data setting.