CHAPTER 11 WATCHDOG TIMER

Preliminary User’s Manual U17260EJ3V1UD

297

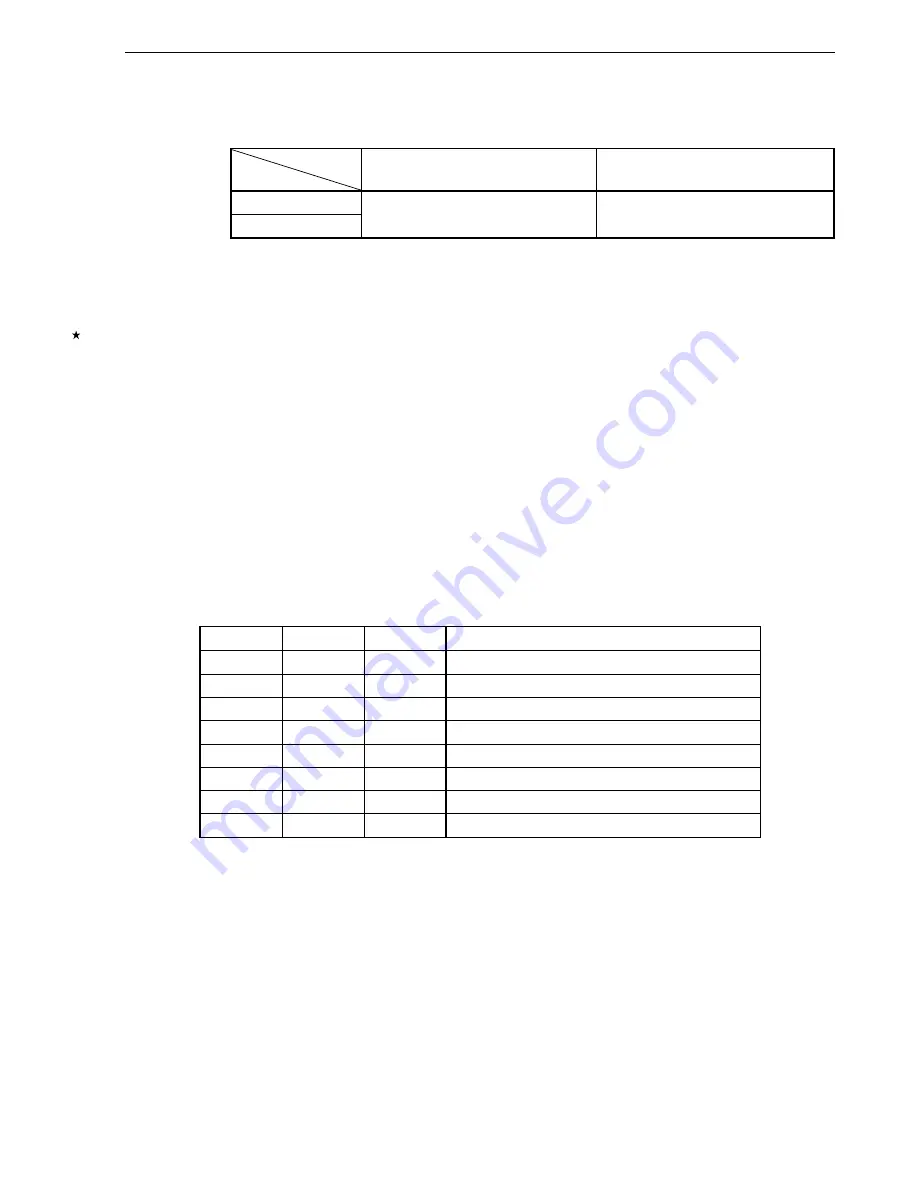

Cautions 4. The operation of the watchdog timer in the HALT and STOP modes differs as follows

depending on the set value of bit 0 (LSROSC) of the option byte.

LSROSC = 0 (Internal Low-Speed

Oscillator Can Be Stopped by Software)

LSROSC = 1 (Internal Low-Speed

Oscillator Cannot Be Stopped)

In HALT mode

In STOP mode

Watchdog timer operation stops.

Watchdog timer operation continues.

If LSROSC = 0, the watchdog timer resumes counting after the HALT or STOP mode is

released. At this time, the counter is not cleared to 0 but starts counting from the value at

which it was stopped.

If oscillation of the internal low-speed oscillator is stopped by setting LSRSTOP (bit 1 of the

internal oscillation mode register (RCM) = 1) when LSROSC = 0, the watchdog timer stops

operating. At this time, the counter is not cleared to 0.

5. The watchdog timer does not stop during self-programming of the flash memory and

EEPROM

TM

emulation. During processing, the interrupt acknowledge time is delayed. Set the

overflow time and window size taking this delay into consideration.

11.4.2 Setting overflow time of watchdog timer

Set the overflow time of the watchdog timer by using bits 3 to 1 (WDCS2 to WDCS0) of the option byte (0080H).

If an overflow occurs, an internal reset signal is generated. The present count is cleared and the watchdog timer

starts counting again by writing “ACH” to WDTE during the window open period before the overflow time.

The following overflow time is set.

Table 11-3. Setting of Overflow Time of Watchdog Timer

WDCS2 WDCS1 WDCS0

Overflow Time of Watchdog Timer

0 0 0

2

10

/f

RL

(3.88 ms)

0 0 1

2

11

/f

RL

(7.76 ms)

0 1 0

2

12

/f

RL

(15.52 ms)

0 1 1

2

13

/f

RL

(31.03 ms)

1 0 0

2

14

/f

RL

(62.06 ms)

1 0 1

2

15

/f

RL

(124.12 ms)

1 1 0

2

16

/f

RL

(248.24 ms)

1 1 1

2

17

/f

RL

(496.48 ms)

Cautions 1. The combination of WDCS2 = WDCS1 = WDCS0 = 0 and WINDOW1 = WINDOW0 = 0

is prohibited.

2. The watchdog timer does not stop during self-programming of the flash memory and

EEPROM emulation. During processing, the interrupt acknowledge time is delayed.

Set the overflow time and window size taking this delay into consideration.

Remarks 1.

f

RL

: Internal low-speed oscillation clock frequency

2.

( ): f

RL

= 264 kHz (MAX.)