5. If the cable is NTT with the connector switch set to 'operate', the test indicator

(TI) signal is not forwarded to the connected DCE, so that the received pattern

differs from the expected one.

Problem Determination Aid for LIC Type 5 and LIC Type 6

Wrap Tests Controlled from the Host

To test the DTE part of a LIC type 5 and LIC type 6, these tests are the same as

for LICs type 1 to LICs type 4. See page 4-93.

Wrap Tests Controlled from the MOSS

To test the DTE part of LICs type 5 and LICs type 6, these tests are the same as

for LICs type 1 to LICs type 4 (see page 4-94). In addtion, the following tests are

available:

Wrap test up to DCE output (with or without line wrap block).

Self-test (which occurs before 'control lead wrap' command takes place).

LIC line analysis procedures (LLAP).

See the

Advanced Operations Guide, and the Problem Determination Guide for

details.

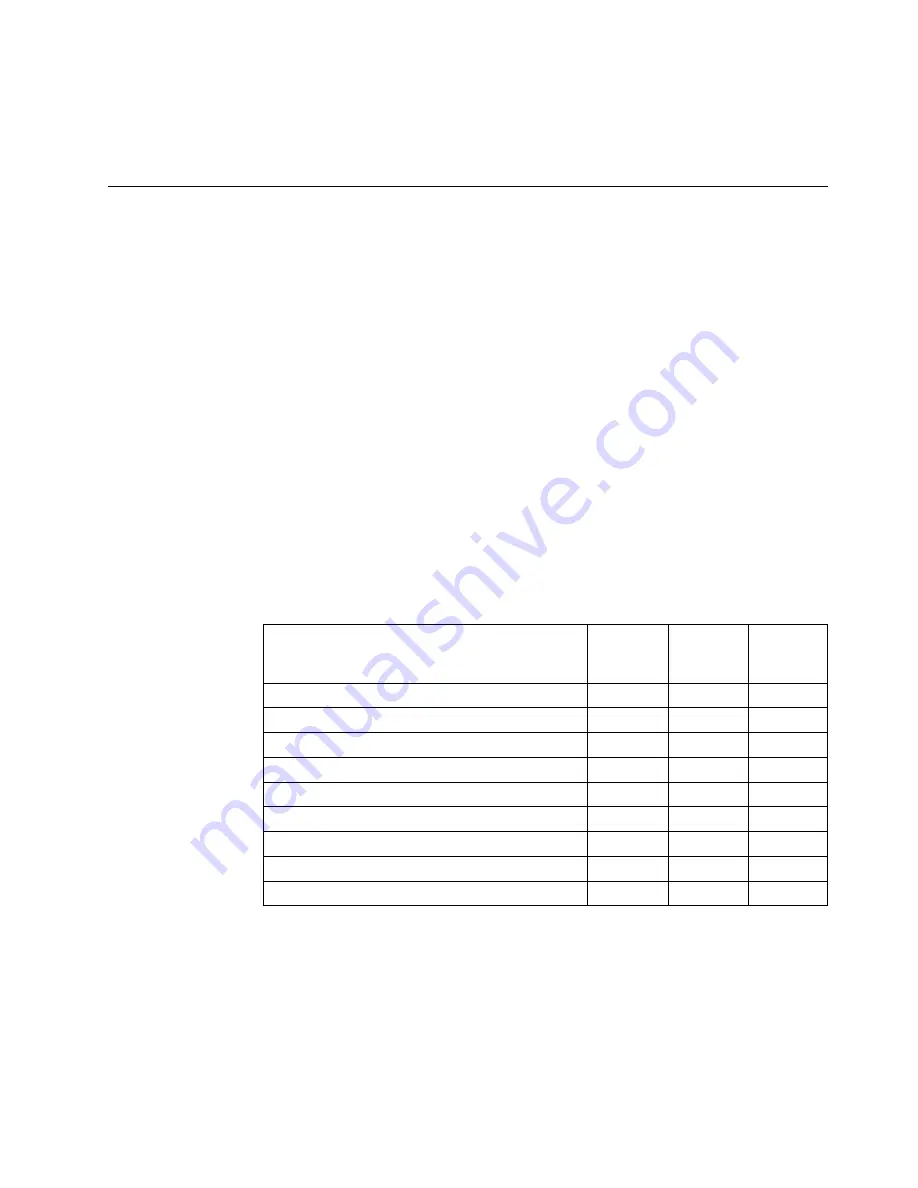

Manual Tests Controlled from the PKD

To test the DCE part of the LIC type 5 and LIC type 6, all the following tests are

manually initiated from the PKD:

Notes:

1. The above tests run continuously until keying 'EXIT'. See the

Connection and

Integration Guide for details.

2. The process of the 'status bits' from the PKD is independent from the LPDA-2.

They are:

Alarm tone received (remote DCE power loss)

Alarm tone received (remote DCE failure)

Carrier loss

Manual Test

Data

Disrup-

tive

LIC

Type 5

LIC

Type 6

Local loop back

Yes

ñ

*

*

Remote loop back

Yes

ñ

*

Local self-test

Yes

ñ

*

*

Local status

No

*

Remote self-test

Yes

*

Remote status

Yes

*

Digital test (transmit/receive test)

Yes

ñ

*

*

Analog test (line analysis)

Yes

*

LIC line analysis procedures (LLAP)

Yes

*

*

Chapter 4. Transmission Subsystem (TSS)

4-95

Summary of Contents for 3745 Series

Page 2: ......

Page 12: ...x IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 14: ...xii IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 18: ...xvi IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 21: ...3745 Models 130 150 160 and 170 Data Flow Chapter 1 General Information 1 3 ...

Page 149: ...For RACs 241 to 244 ERR bits Data received from the adapter Chapter 3 Buses 3 57 ...

Page 166: ...4 14 IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 169: ...Chapter 4 Transmission Subsystem TSS 4 17 ...

Page 322: ...6 28 IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 348: ...7 26 IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 625: ...The ESS in 3745 Models 130 150 160 and 170 Data Flow Chapter 12 Ethernet Subsystem ESS 12 3 ...

Page 674: ...X 6 IBM 3745 Models 130 150 160 170 and 17A Hardware Maintenance Reference ...

Page 708: ......

Page 711: ......

Page 712: ...IBM Part Number 03F5010 Printed in Denmark by IBM Danmark A S ð3F5ð1ð SY33 2ð66 4 ...