324

10.1.2

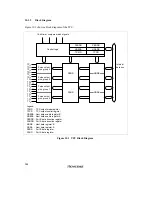

Block Diagram

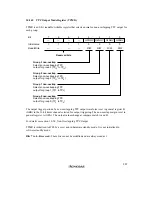

Figure 10.1 shows a block diagram of the TPC.

PADDR

NDERA

TPMR

PBDDR

NDERB

TPCR

Internal

data bus

TP

TP

TP

TP

TP

TP

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Control logic

16-bit timer compare match signals

Pulse output

pins, group 3

PBDR

PADR

Legend:

TPMR

:

TPCR

:

NDERB :

NDERA :

PBDDR :

PADDR :

NDRB

:

NDRA

:

PBDR

:

PADR

:

Pulse output

pins, group 2

Pulse output

pins, group 1

Pulse output

pins, group 0

TPC output mode register

TPC output control register

Next data enable register B

Next data enable register A

Port B data direction register

Port A data direction register

Next data register B

Next data register A

Port B data register

Port A data register

NDRB

NDRA

TP

TP

TP

TP

TP

TP

TP

TP

TP

TP

Figure 10.1 TPC Block Diagram

Summary of Contents for H8/3060

Page 10: ......

Page 16: ......

Page 114: ...66 ...

Page 132: ...84 ...

Page 144: ...96 ...

Page 170: ...122 ...

Page 212: ...164 ...

Page 268: ...220 ...

Page 332: ...284 ...

Page 396: ...348 ...

Page 494: ...446 ...

Page 698: ...650 ...

Page 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Page 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Page 810: ...762 ...

Page 994: ...946 ...