235

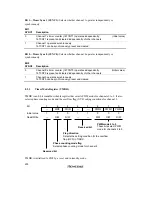

Bit 0—Input Capture/Compare Match Flag A0 (IMFA0): This status flag indicates GRA0

compare match or input capture events.

Bit 0

IMFA0

Description

0

[Clearing condition]

(Initial value)

Read IMFA0 flag when IMFA0 =1, then write 0 in IMFA0 flag

1

[Setting conditions]

•

16TCNT0 = GRA0 when GRA0 functions as an output compare register

•

16TCNT0 value is transferred to GRA0 by an input capture signal when GRA0

functions as an input capture register

8.2.5

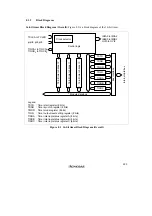

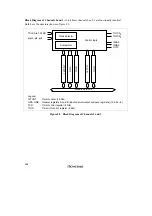

Timer Interrupt Status Register B (TISRB)

TISRB is an 8-bit readable/writable register that indicates GRB compare match or input capture

and enables or disables GRB compare match and input capture interrupt requests.

7

—

1

—

Bit

Initial value

Read/Write

6

IMIEB2

0

R/W

5

IMIEB1

0

R/W

4

IMIEB0

0

R/W

3

—

1

—

2

IMFB2

0

R/(W)

*

1

IMFB1

0

R/(W)

*

0

IMFB0

0

R/(W)

*

Reserved bit

Reserved bit

Input capture/compare match interrupt enable B2 to B0

These bits enable or disable interrupts by the IMFB flags

Input capture/compare match

flags B2 to B0

Status flags indicating GRB

compare match or input capture

Note:

*

Only 0 can be written, to clear the flag.

TISRB is initialized to H'88 by a reset and in standby mode.

Summary of Contents for H8/3060

Page 10: ......

Page 16: ......

Page 114: ...66 ...

Page 132: ...84 ...

Page 144: ...96 ...

Page 170: ...122 ...

Page 212: ...164 ...

Page 268: ...220 ...

Page 332: ...284 ...

Page 396: ...348 ...

Page 494: ...446 ...

Page 698: ...650 ...

Page 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Page 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Page 810: ...762 ...

Page 994: ...946 ...