327

10.2

Register Descriptions

10.2.1

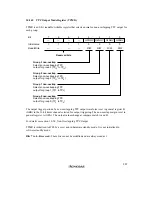

Port A Data Direction Register (PADDR)

PADDR is an 8-bit write-only register that selects input or output for each pin in port A.

Bit

Initial value

Read/Write

7

PA DDR

0

W

Port A data direction 7 to 0

These bits select input or

output for port A pins

7

6

PA DDR

0

W

6

5

PA DDR

0

W

5

4

PA DDR

0

W

4

3

PA DDR

0

W

3

2

PA DDR

0

W

2

1

PA DDR

0

W

1

0

PA DDR

0

W

0

Port A is multiplexed with pins TP

7

to TP

0

. Bits corresponding to pins used for TPC output must

be set to 1. For further information about PADDR, see section 7.11, Port A.

10.2.2

Port A Data Register (PADR)

PADR is an 8-bit readable/writable register that stores TPC output data for groups 0 and 1, when

these TPC output groups are used.

Bit

Initial value

Read/Write

0

PA

0

R/(W)

0

1

PA

0

R/(W)

1

2

PA

0

R/(W)

2

3

PA

0

R/(W)

3

4

PA

0

R/(W)

4

5

PA

0

R/(W)

5

6

PA

0

R/(W)

6

7

PA

0

R/(W)

7

Port A data 7 to 0

These bits store output data

for TPC output groups 0 and 1

*

*

*

*

*

*

*

*

Note: Bits selected for TPC output by NDERA settings become read-only bits.

*

For further information about PADR, see section 7.11, Port A.

Summary of Contents for H8/3060

Page 10: ......

Page 16: ......

Page 114: ...66 ...

Page 132: ...84 ...

Page 144: ...96 ...

Page 170: ...122 ...

Page 212: ...164 ...

Page 268: ...220 ...

Page 332: ...284 ...

Page 396: ...348 ...

Page 494: ...446 ...

Page 698: ...650 ...

Page 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Page 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Page 810: ...762 ...

Page 994: ...946 ...