483

17.3

Flash Memory Register Descriptions

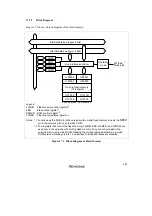

17.3.1

Flash Memory Control Register (FLMCR)

FLMCR is an 8-bit register used for flash memory operating mode control. Program-verify mode

or erase-verify mode is entered by setting SWE to 1 when FWE = 1, then setting the

corresponding bit. Program mode is entered by setting SWE to 1 when FWE = 1, then setting the

PSU bit, and finally setting the P bit. Erase mode is entered by setting SWE to 1 when FWE = 1,

then setting the ESU bit, and finally setting the E bit. FLMCR is initialized by a reset, and in

hardware standby mode and software standby mode. Its initial value is H'80 when a high level is

input to the FWE pin, and H'00 when a low level is input. In mode 6 the FWE pin must be fixed

low, as flash memory on-board programming is not supported. Therefore, bits in this register

cannot be set to 1 in mode 6. When on-chip flash memory is disabled, a read will return H'00, and

writes are invalid. When setting bits 6 to 0 in this register to 1, each bit should be set individually.

Writes to bits ESU, PSU, EV, and PV in FLMCR are enabled only when FWE = 1 and SWE = 1;

writes to the E bit only when FWE = 1, SWE = 1, and ESU = 1; and writes to the P bit only when

FWE = 1, SWE = 1, and PSU = 1.

1/0

R

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

0

R/W

Initial value

Read/Write

7

FWE

0

R

6

SWE

0

R

5

ESU

0

R

4

PSU

0

R

3

EV

0

R

0

P

0

R

2

PV

0

R

1

E

0

R

Bit

Initial value

Read/Write

Modes 5

and 7

Modes 1

to 4, and 6

Program mode

Selects program

mode transition

or clearing

Erase mode

Selects erase mode

transition or clearing

Program-verify mode

Selects program-verify mode

transition or clearing

Erase-verify mode

Selects erase-verify mode transition or clearing

Program setup

Prepares for a transition to program mode

Erase setup

Prepares for a transition to erase mode

Software write enable

Enables or disables programming/erasing

Flash write enable

Sets hardware protection against flash memory programming/erasing

Summary of Contents for H8/3060

Page 10: ......

Page 16: ......

Page 114: ...66 ...

Page 132: ...84 ...

Page 144: ...96 ...

Page 170: ...122 ...

Page 212: ...164 ...

Page 268: ...220 ...

Page 332: ...284 ...

Page 396: ...348 ...

Page 494: ...446 ...

Page 698: ...650 ...

Page 748: ...700 H8 3064F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 8 Sample LED Circuit ...

Page 777: ...729 H8 3062F ZTAT B mask version Ports 1 2 5 LED 600 Ω Figure 22 14 Sample LED Circuit ...

Page 810: ...762 ...

Page 994: ...946 ...