MC96FM204/FM214

April 7, 2016 Ver. 1.8

123

11.9.5 ADC Register Description

The A/D converter control High register (ADCCRH), A/D converter control low register (ADCCRL), Sample and

hold timing data register (SHTDR) and A/D converter data register (ADCDR)

11.9.6 Register Description for ADC

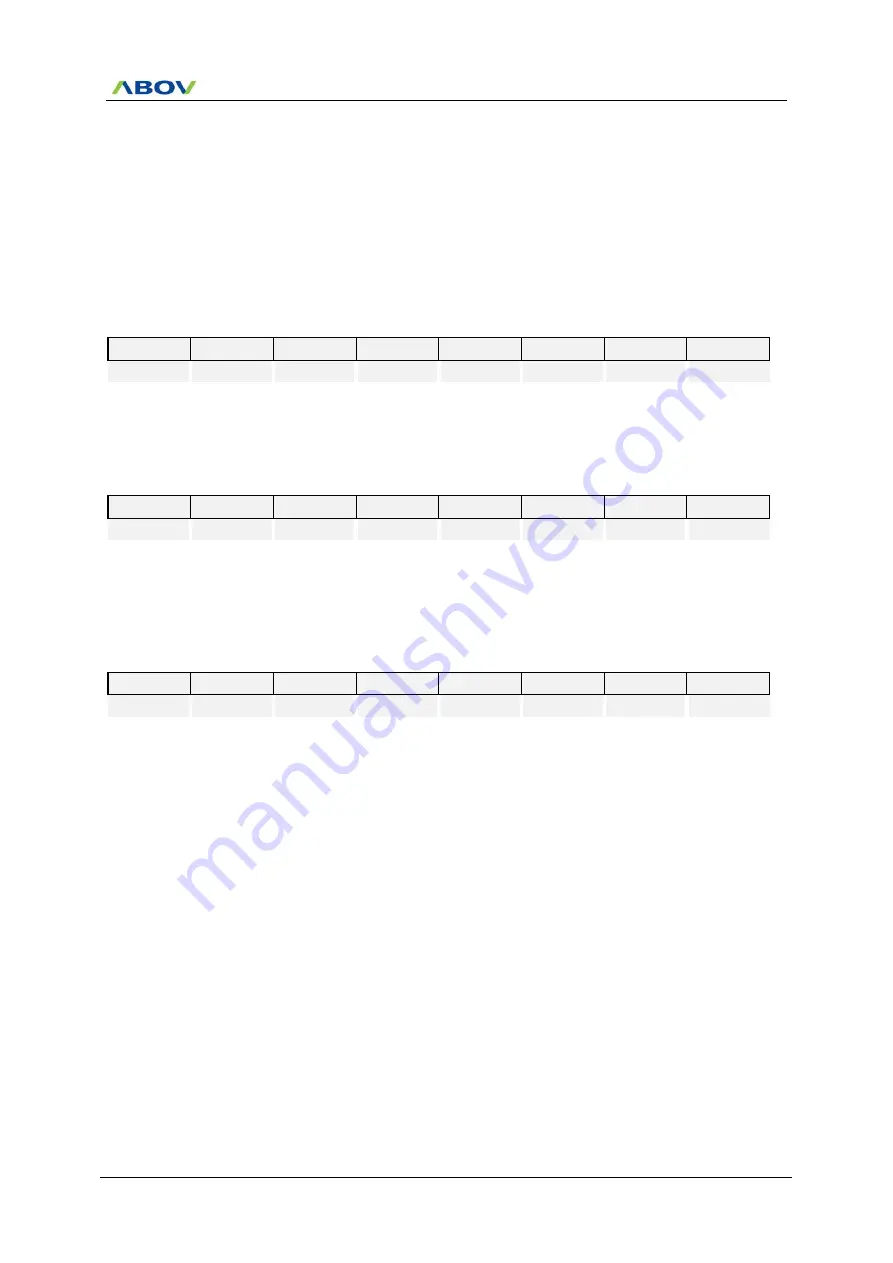

ADCDR (A/D Converter Data Register) : 9CH

7

6

5

4

3

2

1

0

ADCDR7

ADCDR6

ADCDR4

ADCDR4

ADCDR3

ADCDR2

ADCDR1

ADCDR0

R

R

R

R

R

R

R

R

Initial value : xxH

ADCDR[7:0]

A/D Converter Data (8Bit)

SHTDR (Sample and Hold Timing Data Register) : 9DH

7

6

5

4

3

2

1

0

SHTDR7

SHTDR6

SHTDR5

SHTDR4

SHTDR3

SHTDR2

SHTDR1

SHTDR0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value : xxH

SHTDR[7:0]

These bits control the sampling and hold duration. Its resolution is

01H to FFH.

ADCCRH (A/D Converter Control High Register) : 9BH

7

6

5

4

3

2

1

0

–

–

–

SHTRIG1

SHTRIG0

–

CKSEL1

CKSEL0

–

–

–

R/W

R/W

–

R/W

R/W

Initial value : 00H

SHTRIG[1:0]

Sample-and-Hold Trigger Signal Selection

SHTRIG1 SHTRIG0 Description

0

0

ADST

0

1

Timer 0 match signal

1

0

Timer 1 A match signal

1

1

Timer 2 A match signal

CKSEL[1:0]

A/D Converter Clock selection

CKSEL1

CKSEL0

Description

0

0

fx/1

0

1

fx/2

1

0

fx/4

1

1

fx/8

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...