MC96FM204/FM214

April 7, 2016 Ver. 1.8

119

SPICR (SPI Control Register) : B5H

7

6

5

4

3

2

1

0

SPIEN

FLSB

MS

CPOL

CPHA

DSCR

SCR1

SCR0

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

Initial value : 00H

SPIEN

This bit controls the SPI operation

0

Disable SPI operation

1

Enable SPI operation

FLSB

This bit selects the data transmission sequence

0

MSB first mode

1

LSB first mode

MS

This bit selects whether Master or Slave mode

0

Slave mode

1

Master mode

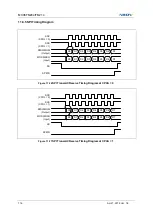

CPOL

CPHA

This two bits control the serial clock (SCK) mode.

Clock polarity (CPOL) bit determine SCK

’s value at idle mode.

Clock phase (CPHA) bit determine if data are sampled on the leading or

trailing edge of SCK.

CPOL CPHA Leading edge

Trailing edge

0

0

Sample (Rising)

Setup (Falling)

0

1

Setup (Rising)

Sample (Falling)

1

0

Sample (Falling)

Setup (Rising)

1

1

Setup (Falling)

Sample (Rising)

DSCR

SCR[1:0]

These three bits select the SCK rate of the device configured as a

master. When DSCR bit is written one, SCK will be doubled in master

mode.

DSCR SCR1

SCR0

SCK frequency

0

0

0

fx/4

0

0

1

fx/16

0

1

0

fx/64

0

1

1

fx/128

1

0

0

fx/2

1

0

1

fx/8

1

1

0

fx/32

1

1

1

fx/64

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...