MC96FM204/FM214

122

April 7, 2016 Ver. 1.8

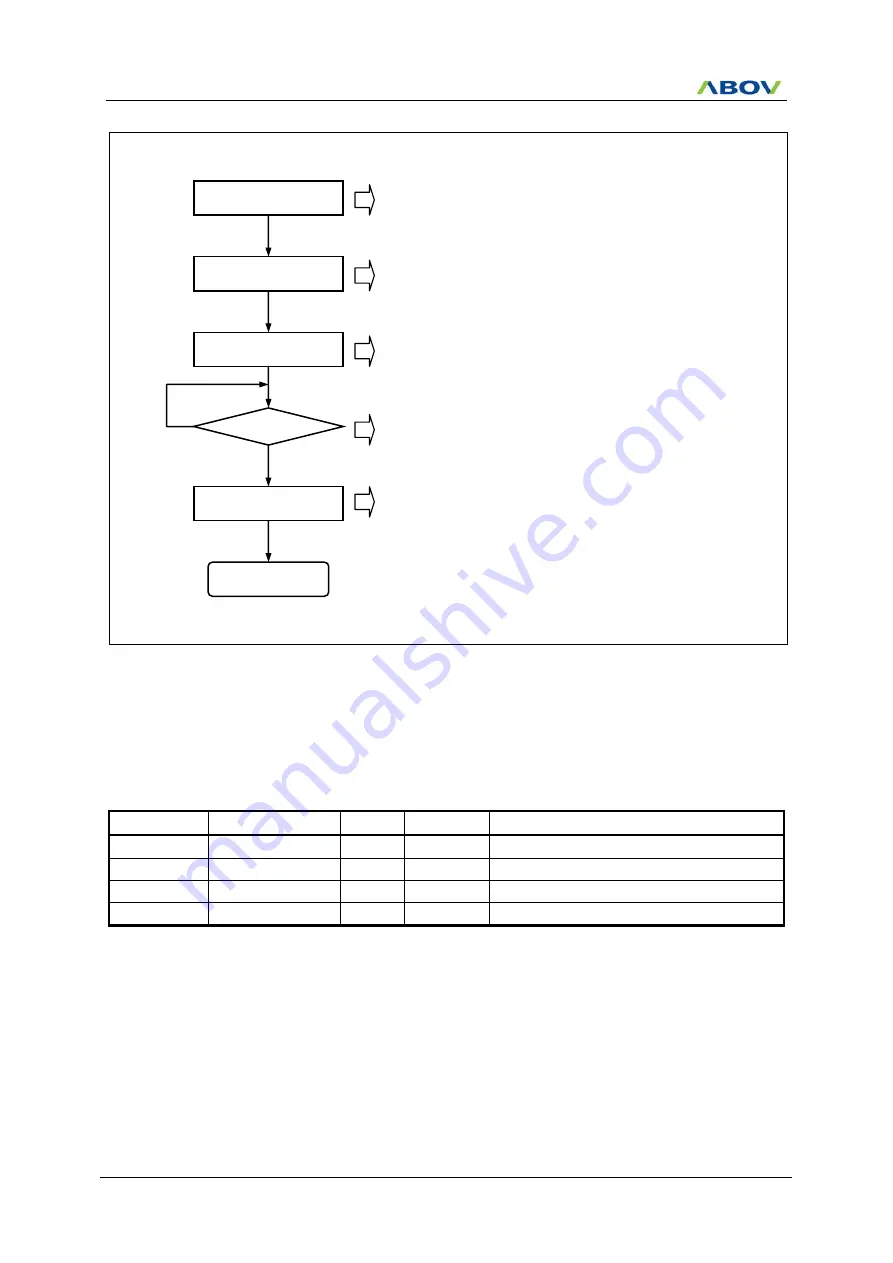

Figure 11.30 A/D Converter Operation Flow

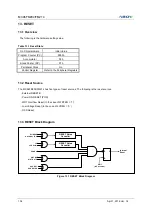

11.9.4 Register Map

Table 11-12 ADC Register Map

Name

Address

Dir

Default

Description

ADCDR

9CH

R

xxH

A/D Converter Data Register

SHTDR

9DH

R/W

FFH

Sample and Hold Timing Data Register

ADCCRH

9BH

R/W

00H

A/D Converter Control High Register

ADCCRL

B0H

R/W

00H

A/D Converter Control Low Register

SET ADCCRH

SET ADCCRL

AFLAG = 1?

Converting

START

READ ADCDR

ADC END

Select ADC Clock

ADC enable & Select AN Input Channel.

Start ADC Conversion.

If Conversion is completed, AFLAG is set

“1” and ADC

interrupt is occurred.

After Conversion is completed, read ADCD

Y

N

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...