MC96FM204/FM214

April 7, 2016 Ver. 1.8

121

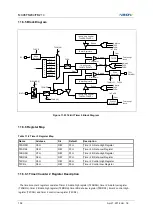

11.9.3 Block Diagram

ADCDR

(Read only)

AN0

AN1

AN5

AN6

AN7

ADCIFR

AFLAG

INT_ACK

Clear

Clear

OP0OUT

To interrupt

block

Pre

Scaler

fx

fx/2

fx/4

fx/8

fx/1

M

U

X

Sample

and

Hold

8-bit SAR

Reference

Voltage

8-bit

Down Counter

CKSEL[1:0]

2

M

U

X

ADSEL[3:0]

4

f

ADCCK

VDD

AVSS

STOP (Power Down)

STBY

Start

SHTDR (8-bit)

M

U

X

SHTRIG[1:0]

2

ADST

T0 match

T1 A match

T2 A match

S

a

m

p

le

H

o

ld

C

o

n

v

e

rt

If > 0, High

If = 0, Low and hold

P

trigger

P

sample

To PGA

block

OP1OUT

Start

Figure 11.28 8-bit ADC Block Diagram

P

trigger

P

sample

f

ADCCK

ADCIFR

Trigger

Signal

Start

Sampling

Stop

Sampling

Start

Conversion

Conversion

Complete

t

sampling

t

conversion

Conversion Clock = 9

Figure 11.29 8-bit A/D Converter Timing Chart

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...