MC96FM204/FM214

April 7, 2016 Ver. 1.8

67

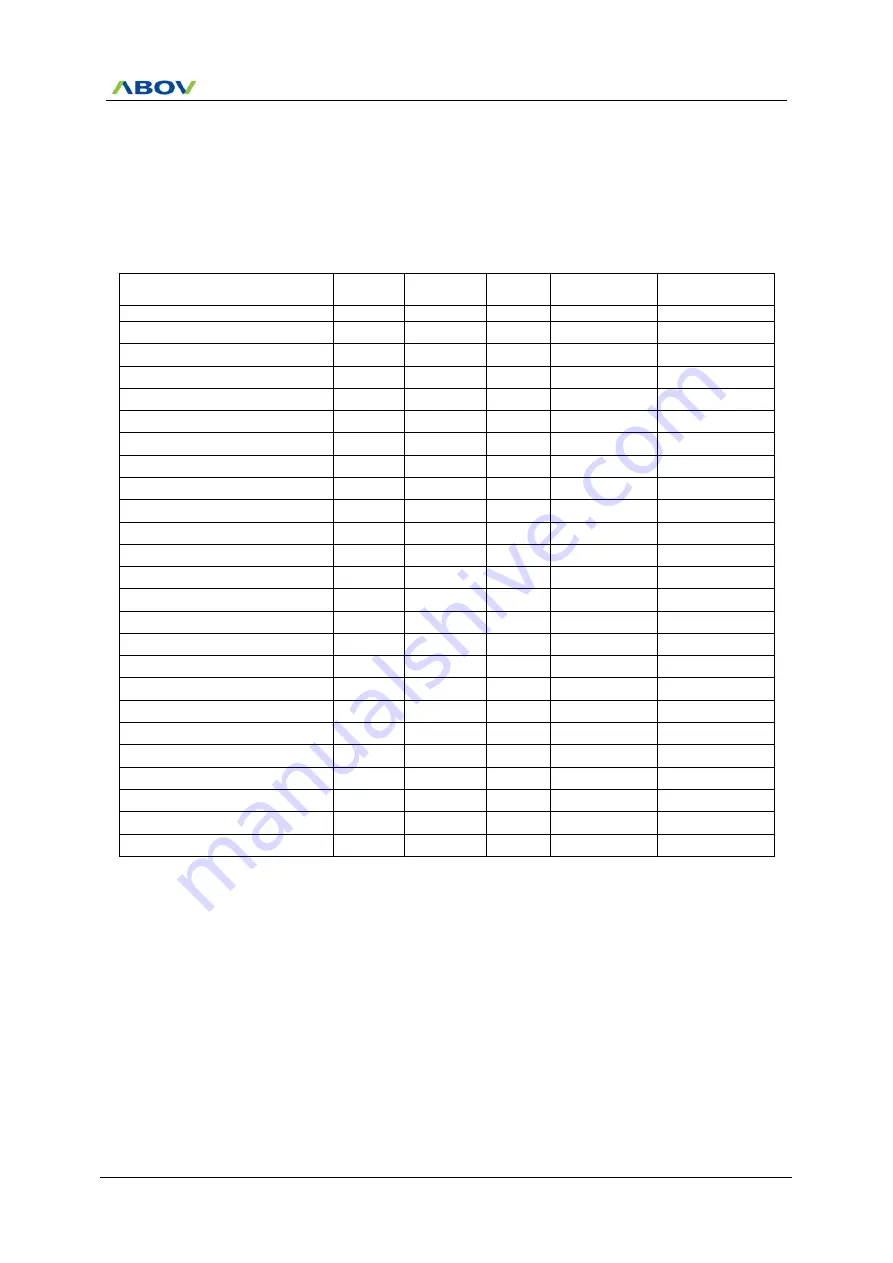

10.4 Interrupt Vector Table

The interrupt controller supports 24 interrupt sources as shown in the Table 10-2. When interrupt is served,

long call instruction (LCALL) is executed and program counter jumps to the vector address. All interrupt requests

have their own priority order.

Table 10-2 Interrupt Vector Address Table

Interrupt Source

Symbol

Interrupt

Enable Bit

Priority

Mask

Vector Address

Hardware Reset

RESETB

0 0

0

Non-Maskable

0000H

External Interrupt 0

INT0

IE.0

1

Maskable

0003H

External Interrupt 1

INT1

IE.1

2

Maskable

000BH

External Interrupt 2

INT2

IE.2

3

Maskable

0013H

External Interrupt 3

INT3

IE.3

4

Maskable

001BH

External Interrupt 11

INT4

IE.4

5

Maskable

0023H

External Interrupt 12

INT5

IE.5

6

Maskable

002BH

–

INT6

IE1.0

7

Maskable

0033H

–

INT7

IE1.1

8

Maskable

003BH

–

INT8

IE1.2

9

Maskable

0043H

ADC Interrupt

INT9

IE1.3

10

Maskable

004BH

Comparator Interrupt

INT10

IE1.4

11

Maskable

0053H

SPI Interrupt

INT11

IE1.5

12

Maskable

005BH

T0 Interrupt

INT12

IE2.0

13

Maskable

0063H

T1 Interrupt

INT13

IE2.1

14

Maskable

006BH

–

INT14

IE2.2

15

Maskable

0073H

–

INT15

IE2.3

16

Maskable

007BH

T2 Interrupt

INT16

IE2.4

17

Maskable

0083H

–

INT17

IE2.5

18

Maskable

008BH

–

INT18

IE3.0

19

Maskable

0093H

WDT Interrupt

INT19

IE3.1

20

Maskable

009BH

BIT Interrupt

INT20

IE3.2

21

Maskable

00A3H

–

INT21

IE3.3

22

Maskable

00ABH

–

INT22

IE3.4

23

Maskable

00B3H

–

INT23

IE3.5

24

Maskable

00BBH

For maskable interrupt execution, EA bit must set ‘1’ and specific interrupt must be enabled by writing ‘1’ to

associated bit in the IEx. If an interrupt request is received, the specific interrupt request flag is set to

‘1’. And it

remains ‘1’ until CPU accepts interrupt. If the interrupt is served, the interrupt request flag will be cleared

automatically.

10.5 Interrupt Sequence

An interrupt request is held

until the interrupt is accepted or the interrupt latch is cleared to ‘0’ by a reset or an

instruction. Interrupt acceptance always generates at last cycle of the instruction. So instead of fetching the

current instruction, CPU executes internally LCALL instruction and saves the PC at stack. For the interrupt

service routine, the interrupt controller gives the address of LJMP instruction to CPU. Since the end of the

execution of current instruction, it needs 3~9 machine cycles to go to the interrupt service routine. The interrupt

service task is terminated by the interrupt return instruction [RETI]. Once an interrupt request is generated, the

following process is performed.

Summary of Contents for MC96FM204

Page 17: ...MC96FM204 FM214 April 7 2016 Ver 1 8 17 4 Package Diagram Figure 4 1 20 Pin SOP Package ...

Page 18: ...MC96FM204 FM214 18 April 7 2016 Ver 1 8 Figure 4 2 20 Pin TSSOP Package ...

Page 19: ...MC96FM204 FM214 April 7 2016 Ver 1 8 19 Figure 4 3 16 Pin SOP Package ...

Page 20: ...MC96FM204 FM214 20 April 7 2016 Ver 1 8 Figure 4 4 16 Pin TSSOP Package ...