SmartTime Static Timing Analyzer User Guide

56

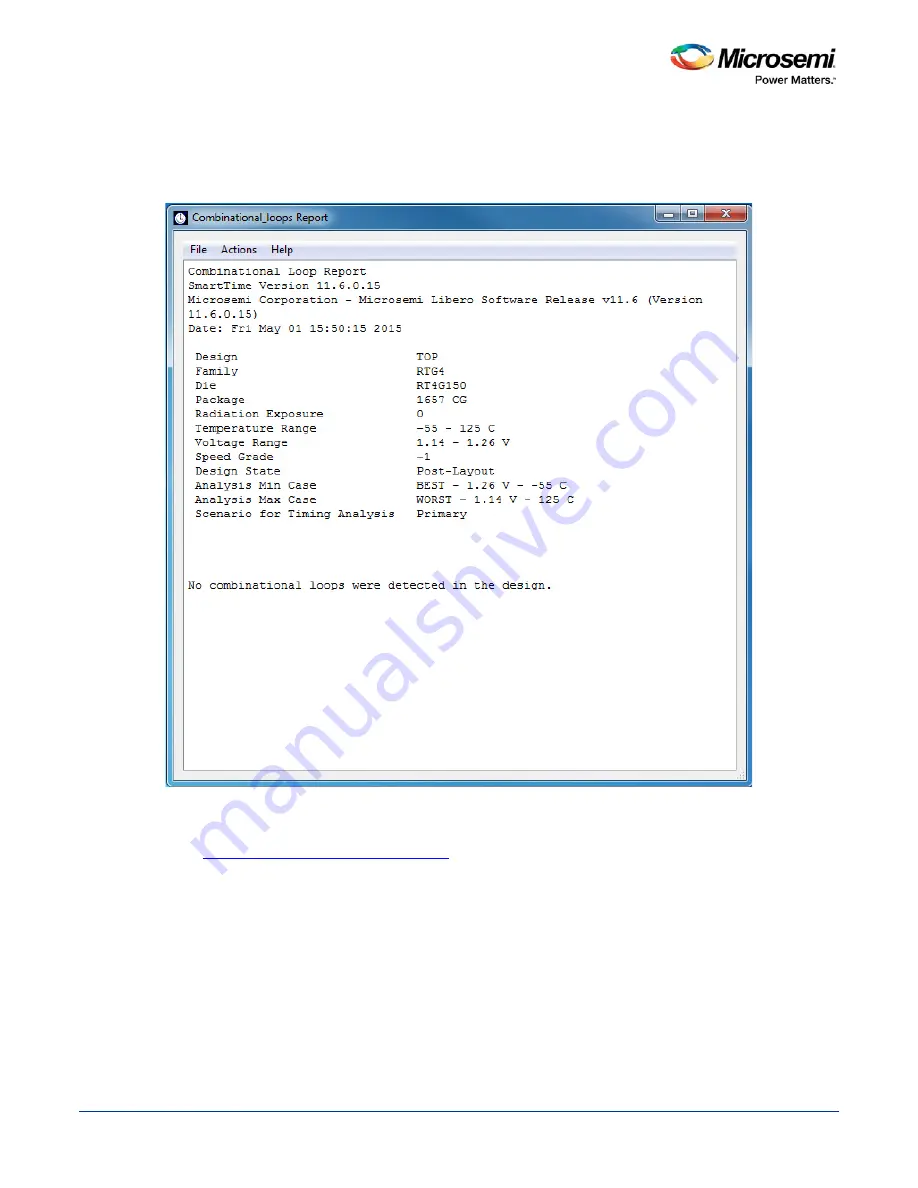

Understanding Combinational Loop Reports

The combinational loop report displays all loops found during initialization and reports pins associated with

the loop(s), and the location where the loop is broken.

Figure 28 · Combinational Loop Report

See Also

Generating a Combinational Loop Report

Содержание SmartTime

Страница 2: ......

Страница 6: ......

Страница 15: ...SmartTime Static Timing Analyzer User Guide 15 SmartTime Timing Analyzer ...

Страница 31: ...SmartTime Static Timing Analyzer User Guide 31 Advanced Timing Analysis ...

Страница 37: ...SmartTime Static Timing Analyzer User Guide 37 Generating Timing Reports ...

Страница 57: ...SmartTime Static Timing Analyzer User Guide 57 Timing Concepts ...

Страница 66: ...SmartTime Static Timing Analyzer User Guide 66 ...

Страница 91: ...SmartTime Static Timing Analyzer User Guide 91 Q_reg NOT2 end not u1 NOT1 MUX2 not u2 NOT2 NOT1 endmodule ...

Страница 92: ...SmartTime Static Timing Analyzer User Guide 92 Dialog Boxes ...

Страница 118: ...SmartTime Static Timing Analyzer User Guide 118 Tcl Commands ...